QSpan<sup>тм</sup> (СА91С860В, СА91L860В)

PCI to Motorola Processor Bridge Manual

http://www.tundra.com

The information in this document is subject to change without notice and should not be construed as a commitment by Tundra Semiconductor Corporation. While reasonable precautions have been taken, Tundra Semiconductor Corporation assumes no responsibility for any errors that may appear in this document.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Tundra Semiconductor Corporation.

Tundra® products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Tundra product could create a situation where personal injury or death may occur. Should Buyer purchase or use Tundra products for any such unintended or unauthorized application, Buyer shall indemnify and hold Tundra and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Tundra was negligent regarding the design or manufacture of the part.

The acceptance of this document will be construed as an acceptance of the foregoing conditions.

QSpan<sup>TM</sup> PCI to Motorola Processor Bridge Manual

Copyright 1999, Tundra Semiconductor Corporation All rights reserved.

Document: 8091860.MD302.05

Printed in Canada

Tundra and Tundra logo are registered trademarks of Tundra Semiconductor Corporation. QSpan is a trademark of Tundra Semiconductor Corporation.

## **Overview**

- Chapter 1 General Information

- Chapter 2 Functional Description

- Chapter 3 Description of Signals

- Chapter 4 Signals and DC Characteristics

- Appendix A Registers

- Appendix B Timing

- **Appendix C** Typical Applications

- Appendix D Initialization

- Appendix E Endian Mapping

- Appendix F Operating and Storage Conditions

- Appendix G Mechanical and Ordering Information

iv

## **Table of Contents**

For the latest QSpan documentation, including: application notes, user manual, manual addenda, reference design manual, etc., please visit our web site: **http://www.tundra.com**

| 1       | General Information 1-1                           |

|---------|---------------------------------------------------|

| 1.1     | Introduction 1-1                                  |

| 1.2     | Product Overview 1-2                              |

| 1.3     | Using This Document 1-2                           |

| 1.4     | Revision History 1-3                              |

| 1.5     | Conventions 1-4                                   |

| 1.5.1   | Signals1-4                                        |

| 1.5.2   | Terminology1-4                                    |

| 1.5.3   | Symbols1-5                                        |

| 1.6     | QSpan Technical Support and Documentation 1-5     |

| 2       | Functional Description 2-1                        |

| 2.1     | Architectural Overview                            |

| 2.1.1   | The QBus Slave Channel: From Processor to PCI Bus |

| 2.1.2   | The PCI Target Channel: From PCI Bus to QBus      |

| 2.1.3   | The IDMA Channel                                  |

| 2.1.4   | The Register Channel2-4                           |

| 2.1.5   | The Interrupt Channel                             |

| 2.1.6   | The EEPROM Channel                                |

| 2.2     | The QBus Slave Channel 2-5                        |

| 2.2.1   | QBus Slave Channel Architecture Overview2-6       |

| 2.2.1.1 | QBus Slave Module 2-7                             |

| 2.2.1.2 | Qx-FIFO and Qr-FIFO                               |

| 2.2.1.3 | PCI Master Module 2-7                             |

| 2.2.2   | Overview of Channel Description2-8                |

| 2.2.3   | Address Phase                                     |

| 2.2.3.1 | Transaction decoding and QBus Slave Images 2-8    |

| 2.2.3.1.1   | PowerQUICC Cycles                          | 2-10 |

|-------------|--------------------------------------------|------|

| 2.2.3.1.2   | QUICC Cycles                               | 2-11 |

| 2.2.3.1.3   | M68040 Cycles                              | 2-11 |

| 2.2.3.2     | PCI Bus Request                            | 2-11 |

| 2.2.3.3     | Address Translation                        | 2-12 |

| 2.2.3.4     | Address Phase on the PCI Bus               | 2-13 |

| 2.2.4       | Data Transfer                              | 2-15 |

| 2.2.4.1     | Endian Mapping                             | 2-15 |

| 2.2.4.2     | Data Path                                  | 2-18 |

| 2.2.4.2.1   | Writes                                     | 2-18 |

| 2.2.4.2.2   | Read Transactions (Burst and Single Cycle) | 2-19 |

| 2.2.4.2.3   | Delayed Reads and PCI Transaction Ordering | 2-19 |

| 2.2.4.3     | PCI Target Channel Reads                   | 2-20 |

| 2.2.4.4     | Parity Monitoring by PCI Master Module     | 2-20 |

| 2.2.5       | Termination Phase                          | 2-21 |

| 2.2.5.1     | Posted Writes                              | 2-23 |

| 2.3         | The PCI Target Channel                     | 2-24 |

| 2.3.1       | PCI Target Channel Architecture Overview   | 2-25 |

| 2.3.1.1     | PCI Target Module                          | 2-25 |

| 2.3.1.2     | Px-FIFO and Pr-FIFO                        | 2-26 |

| 2.3.1.3     | QBus Master Module                         | 2-26 |

| 2.3.2       | Overview of Channel Description            | 2-26 |

| 2.3.3       | Address Phase                              | 2-27 |

| 2.3.3.1     | Transaction Decoding                       | 2-27 |

| 2.3.3.2     | Address Translation                        | 2-30 |

| 2.3.3.3     | Transaction Codes on the QBus              | 2-32 |

| 2.3.3.4     | PCI BIOS Memory Allocation                 | 2-32 |

| 2.3.4       | Data Transfer                              | 2-33 |

| 2.3.4.1     | Endian Mapping                             | 2-33 |

| 2.3.4.1.1   | Write Cycle Mapping for PCI Target Channel | 2-34 |

| 2.3.4.1.1.1 | 32-Bit QBus Port                           | 2-34 |

| 2.3.4.1.1.2 | 16-Bit QBus Port                                    | 2-35   |

|-------------|-----------------------------------------------------|--------|

| 2.3.4.1.1.3 | 8-bit QBus port                                     | 2-35   |

| 2.3.4.1.2   | Read Cycle Mapping for PCI Target Channel           | 2-36   |

| 2.3.4.1.2.1 | 32-bit QBus Port                                    | 2-36   |

| 2.3.4.1.2.2 | 16-Bit QBus Port                                    | 2-37   |

| 2.3.4.1.2.3 | 8-Bit QBus Port                                     | 2-38   |

| 2.3.4.2     | Data Path                                           | 2-39   |

| 2.3.4.2.1   | Posted Writes                                       | 2-39   |

| 2.3.4.2.1.1 | Acceptance of Burst Writes by the PCI Target Module | 2-39   |

| 2.3.4.2.1.2 | Bursting on the QBus                                | 2-40   |

| 2.3.4.2.2   | Delayed Writes                                      | 2-41   |

| 2.3.4.2.3   | Single Read Transactions                            | 2-41   |

| 2.3.4.2.4   | Pre-fetched Read Transactions                       | 2-41   |

| 2.3.4.3     | Parity Monitoring by PCI Target Module              | 2-42   |

| 2.3.5       | Reads and PCI Transaction Ordering                  | . 2-43 |

| 2.3.6       | QBus Arbitration and Sampling                       | . 2-43 |

| 2.3.6.1     | QUICC Bus Arbitration                               | 2-43   |

| 2.3.6.2     | PowerQUICC Bus Arbitration                          | 2-44   |

| 2.3.6.3     | M68040 Bus Arbitration                              | 2-44   |

| 2.3.7       | Terminations                                        | . 2-45 |

| 2.3.7.1     | QBus Master Module Terminations                     | 2-45   |

| 2.3.7.2     | QUICC Cycle Terminations                            | 2-45   |

| 2.3.7.3     | PowerQUICC Cycle Terminations                       | 2-46   |

| 2.3.7.4     | M68040 Cycle Terminations                           | 2-46   |

| 2.3.7.5     | Terminations driven by the PCI Target Module        | 2-46   |

| 2.3.7.6     | Posted Writes                                       | 2-48   |

| 2.4         | The IDMA Channel                                    | 2-49   |

| 2.4.1       | PCI Read Transactions                               | 2-50   |

| 2.4.2       | PCI Write Transactions                              | 2-51   |

| 2.4.3       | TC[3:0] Encoding with PowerQUICC IDMA               | . 2-53 |

| 2.4.4       | IDMA Status Tracking                                | 2-53   |

| 2.4.5     | IDMA Errors, Resets and Interrupts                  |      |

|-----------|-----------------------------------------------------|------|

| 2.4.6     | IDMA Endian Issues                                  |      |

| 2.5       | The Register Channel                                | 2-58 |

| 2.5.1     | Register Access from the PCI Bus                    |      |

| 2.5.2     | Register Access from the QBus                       |      |

| 2.5.2.1   | Examples of QBus Register Accesses                  | 2-61 |

| 2.5.2.2   | PCI Configuration Cycles Generated from the QBus    | 2-62 |

| 2.5.2.2.1 | Address Phase of PCI Configuration Cycles           | 2-62 |

| 2.5.2.2.2 | Data Phase of PCI Configuration Cycles              | 2-63 |

| 2.5.2.3   | Interrupt Acknowledge Cycle                         | 2-64 |

| 2.6       | The Interrupt Channel                               | 2-64 |

| 2.6.1     | Register Access Synchronization                     |      |

| 2.6.2     | Hardware Triggered Interrupts                       |      |

| 2.6.3     | Software Triggered Interrupts                       |      |

| 2.6.4     | Interrupt Acknowledge Cycle                         |      |

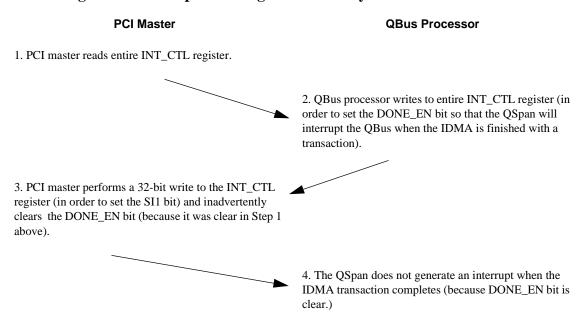

| 2.7       | The EEPROM Channel                                  | 2-69 |

| 2.7.1     | EEPROM Configuration and Plug 'n Play Compatibility |      |

| 2.7.2     | EEPROM I <sup>2</sup> C protocol                    |      |

| 2.7.3     | Mapping of EEPROM Bits to QSpan Registers           |      |

| 2.7.4     | Programming the EEPROM from the QBus or PCI Bus     |      |

| 2.7.4.1   | Writing to the EEPROM                               | 2-73 |

| 2.7.4.2   | Reading from the EEPROM                             | 2-74 |

| 2.8       | Reset Options                                       | 2-75 |

| 2.8.1     | Resets                                              |      |

| 2.8.1.1   | PCI Transactions During QBus Reset                  | 2-76 |

| 2.8.1.2   | IDMA Reset                                          | 2-76 |

| 2.8.1.3   | Clocking and Resets                                 | 2-76 |

| 2.8.2     | Reset Options                                       |      |

| 2.8.2.1   | PCI Bus Master Reset Options                        | 2-77 |

| 2.8.2.2   | QBus Master and Slave Modes                         | 2-77 |

| 2.8.2.3   | EEPROM Loading                                      | 2-78 |

| 2.9         | Hardware Implementation Issues           |          |

|-------------|------------------------------------------|----------|

| 2.9.1       | Test Mode Pins                           |          |

| 2.9.2       | JTAG Support                             |          |

| 2.9.3       | Decoupling Capacitors                    |          |

| 3           | Description of Signals                   |          |

| 3.1         | QUICC Signals                            |          |

| 3.2         | PowerQUICC Signals                       |          |

| 3.3         | M68040 Signals                           |          |

| 3.4         | PCI Bus Signals                          |          |

| 3.5         | Miscellaneous Signals                    |          |

| 3.6         | JTAG Signals                             |          |

| 4           | Signals and DC Characteristics           | 4-1      |

| 4.1         | Terminology                              |          |

| 4.2         | Packaging and Voltage Level Support      |          |

| 4.3         | Signals and DC Characteristics           |          |

| 4.3.1       | PBGA Electrical Characteristics          |          |

| 4.3.2       | PQFP Electrical Characteristics          |          |

| 4.3.3       | AC Signal Characteristics                |          |

| Append      | lix A – Registers                        | App A-1  |

| Append      | dix B – Timing                           | App B-1  |

| <b>B</b> .1 | Timing Parameters                        | App B-1  |

| B.2         | Wait State Insertion (QBus Slave Module) | App B-19 |

| B.3         | Timing Diagrams                          | App B-20 |

| B.3.1       | QBus (QUICC) Interface                   | App B-20 |

| B.3.1.1     | QBus (QUICC) Master Cycles               | App B-20 |

| B.3.1.2     | QBus (QUICC) Slave Cycles                | App B-23 |

| B.3.1.3     | QBus (QUICC) IDMA Cycles                 | App B-27 |

| B.3.2       | QBus (PowerQUICC) Interface              | App B-36 |

| B.3.2.1     | QBus (PowerQUICC) Master Cycles          | App B-36 |

| B.3.2.2  | QBus (PowerQUICC) Slave Cycle    | App B-41 |

|----------|----------------------------------|----------|

| B.3.2.3  | QBus (PowerQUICC) IDMA Cycles    | App B-47 |

| B.3.3    | QBus (M68040) Interface          | App B-52 |

| B.3.3.1  | QBus (M68040) Master Cycles      | App B-52 |

| B.3.3.2  | QBus (M68040) Slave Cycles       | App B-55 |

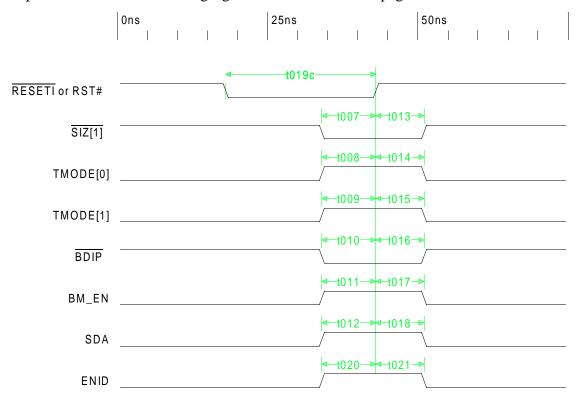

| B.3.4    | Utility Functions                | App B-61 |

| B.3.5    | Reset Options                    | App B-63 |

| Appendix | C – Typical Applications         | App C-1  |

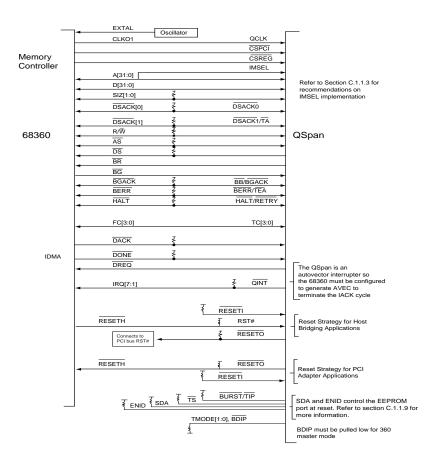

| C.1      | QUICC Interface                  | App C-1  |

| C.1.1    | Hardware Interface               | App C-2  |

| C.1.1.1  | Clocking                         | App C-2  |

| C.1.1.2  | Resets                           | App C-2  |

| C.1.1.3  | Memory Controller                | App C-2  |

| C.1.1.4  | Qbus Direct Connects             | App C-3  |

| C.1.1.5  | Interrupts                       | App C-3  |

| C.1.1.6  | PCI Signals                      | App C-3  |

| C.1.1.7  | EEPROM Interface                 | App C-4  |

| C.1.1.8  | Reset Options                    | App C-4  |

| C.1.1.9  | Unused Inputs Requiring Pull-Ups | App C-5  |

| C.1.1.10 | No Connects                      | App C-5  |

| C.1.1.11 | JTAG Signals                     | App C-5  |

| C.1.1.12 | Address Multiplexing for DRAM    | App C-5  |

| C.1.2    | Software Issues                  | App C-5  |

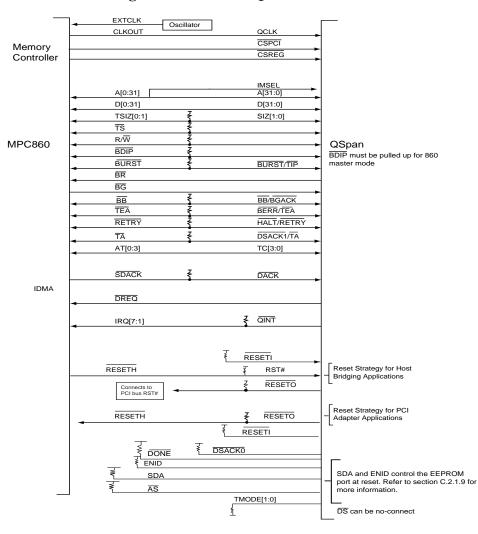

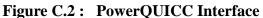

| C.2      | PowerQUICC Interface             | App C-6  |

| C.2.1    | Hardware Interface               | App C-7  |

| C.2.1.1  | Clocking                         | App C-7  |

| C.2.1.2  | Resets                           | App C-7  |

| C.2.1.3  | Memory Controller                | App C-8  |

| C.2.1.4  | QBus Direct Connects             | App C-8  |

| C.2.1.5  | Interrupts                       | App C-8  |

| C.2.1.6  | PCI Signals                      | App C-8  |

| C.2.1.7    | EEPROM Interface                    | App C-9  |

|------------|-------------------------------------|----------|

| C.2.1.8    | Reset Options                       | App C-9  |

| C.2.1.9    | Unused Inputs Requiring Pull-Ups    | App C-10 |

| C.2.1.10   | No Connects                         | App C-10 |

| C.2.1.11   | JTAG Signals                        | App C-10 |

| C.2.1.12   | Bused Signals                       | App C-10 |

| C.2.1.13   | Multiplexing for DRAM               | App C-10 |

| C.2.2      | Software Issues                     | App C-10 |

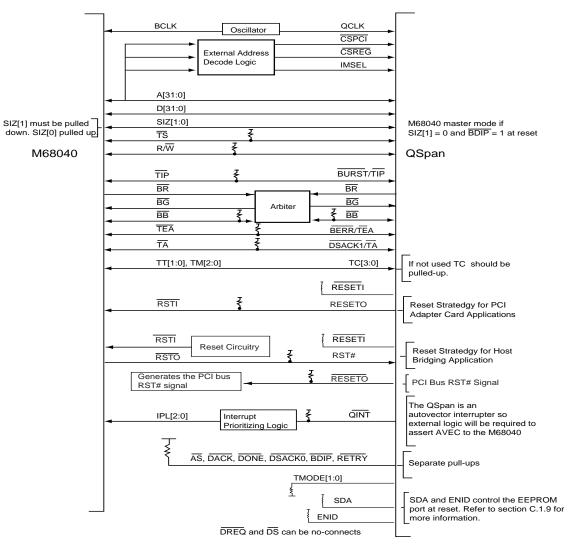

| C.3        | M68040 Interface                    | App C-12 |

| C.3.1      | Hardware Interface                  | App C-12 |

| C.3.1.1    | Clocking                            | App C-13 |

| C.3.1.2    | Resets                              | App C-13 |

| C.3.1.3    | Address Decoder                     | App C-13 |

| C.3.1.4    | QBus Direct Connects                | App C-14 |

| C.3.1.5    | Interrupts                          | App C-14 |

| C.3.1.6    | PCI Signals                         | App C-14 |

| C.3.1.7    | EEPROM Interface                    | App C-15 |

| C.3.1.8    | Reset Options                       | App C-15 |

| C.3.1.9    | Unused Inputs Requiring Pull-Ups    | App C-15 |

| C.3.1.10   | No Connects                         | App C-16 |

| C.3.1.11   | JTAG Signals                        | App C-16 |

| Appendix I | D – Initialization                  | App D-1  |

| D.1        | Hardware Configuration              | App D-1  |

| D.2        | QSpan Register Configuration        | App D-1  |

| D.2.1      | QBus Slave Channel Initialization   | App D-2  |

| D.2.2      | Register Access From the PCI Bus    | App D-3  |

| D.2.3      | PCI Target Channel Initialization   | App D-3  |

| D.2.3.1    | Error Logging and Interrupts        | App D-5  |

| D.2.4      | IDMA Channel Initialization         | App D-5  |

| D.2.5      | General Purpose Software Interrupts | App D-7  |

| D.2.6      | PCI Interface—Miscellaneous         | App D-8  |

| D.2.6.1    | Generation of PCI Configuration and IACK Cycles | App D-8 |

|------------|-------------------------------------------------|---------|

| D.2.6.2    | PCI Expansion ROM Implementation                | App D-9 |

| D.3        | EEPROM                                          | App D-9 |

| Appendix l | E – Endian Mapping                              | App E-1 |

| Appendix l | F – Operating and Storage Conditions            | App F-1 |

| F.1        | 5 Volts Data                                    | App F-1 |

| F.1.1      | Thermal Characteristics                         | App F-2 |

| F.2        | 3.3 Volt Data                                   | App F-3 |

| F.2.1      | Thermal Characteristics                         | App F-4 |

| Appendix ( | G – Mechanical and Ordering Information         | App G-1 |

| G.1        | Mechanical Information                          | App G-1 |

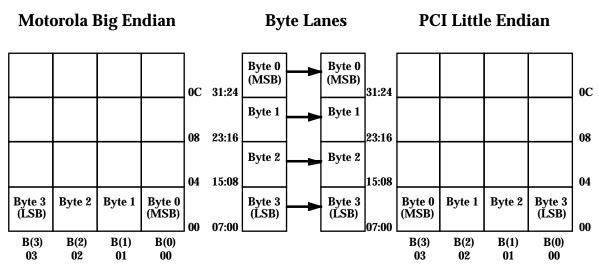

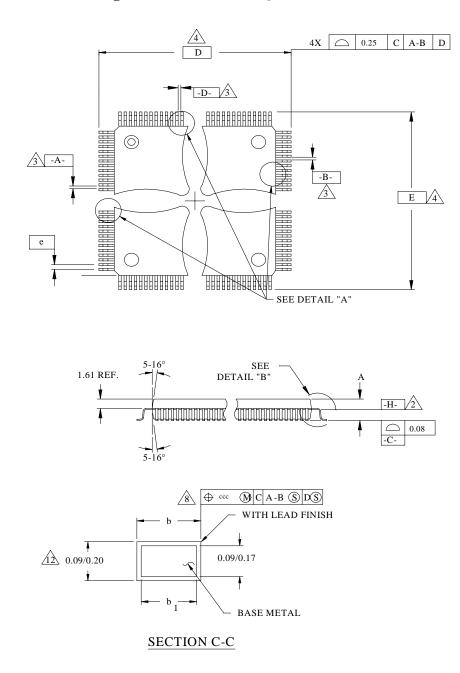

| G.1.1      | 208 PQFP                                        | App G-1 |

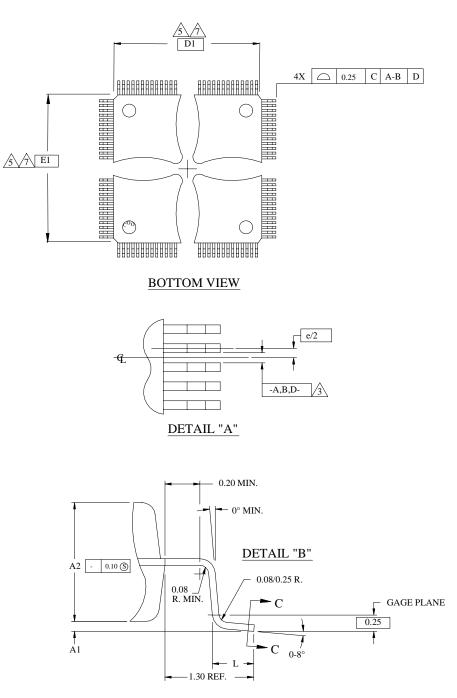

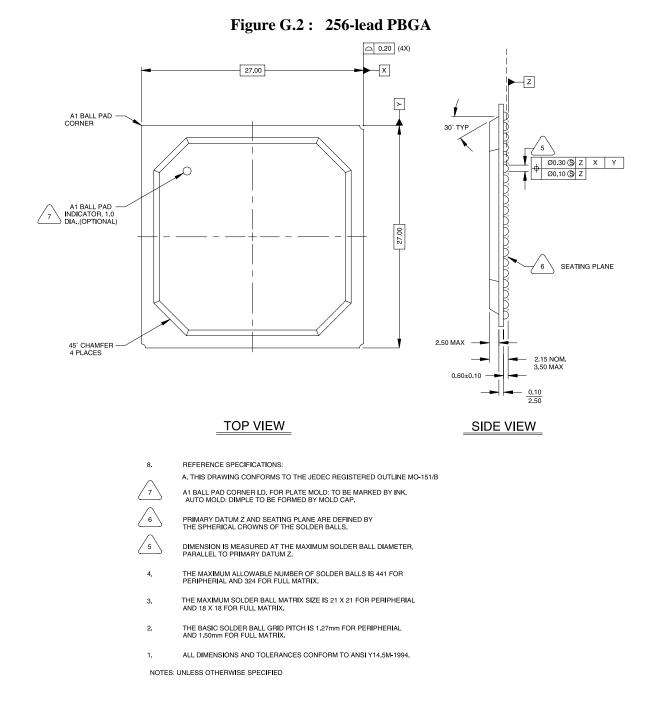

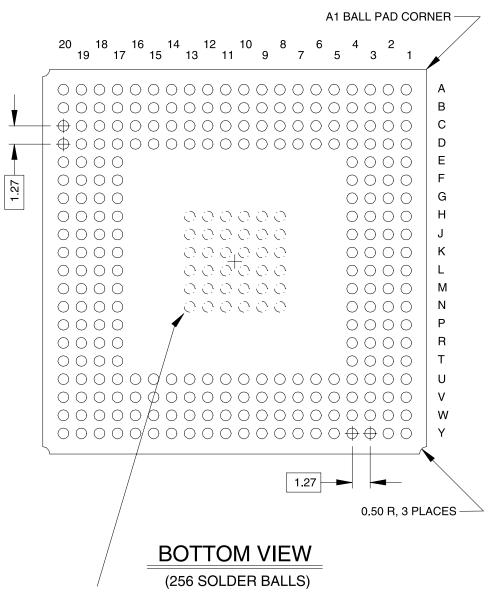

| G.1.2      | 256 PBGA                                        | App G-4 |

| G.2        | Ordering Information                            | App G-6 |

| Index      |                                                 | Index-1 |

| WorldWid   | e Sales Network                                 | Sales-1 |

# **List of Figures**

| Figure 1.1    | The QSpan Bridging PCI and Processor Buses 1-1                    |

|---------------|-------------------------------------------------------------------|

| Figure 2.1    | QSpan Functional Block Diagram 2-2                                |

| Figure 2.2    | QBus Slave Channel in Context 2-6                                 |

| Figure 2.3    | Address Generator for QBus Slave Channel Transfers 2-12           |

| Figure 2.4    | PCI Target Channel 2-25                                           |

| Figure 2.5    | Address Generator for PCI Target Channel Transfers 2-30           |

| Figure 2.6    | .QSpan Control and Status Registers                               |

| Figure 2.7    | PCI Access to QCSR in Memory Space 2-59                           |

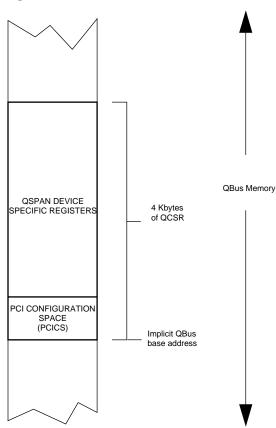

| Figure 2.8    | QCSR Access from the QBus 2-61                                    |

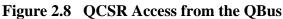

| Figure 2.9    | Example of a Register-Access Synchronization Problem 2-65         |

| Figure 2.10   | Sequential Read from EEPROM 2-70                                  |

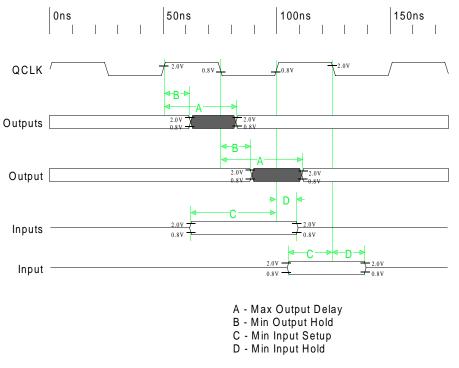

| Figure B.1 :  | Reference Voltages for AC Timing Specification App B-2            |

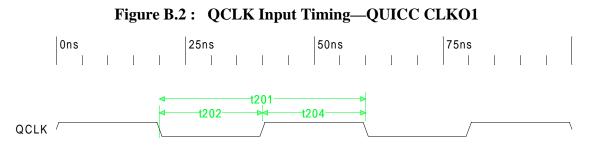

| Figure B.2 :  | QCLK Input Timing—QUICC CLKO1 App B-20                            |

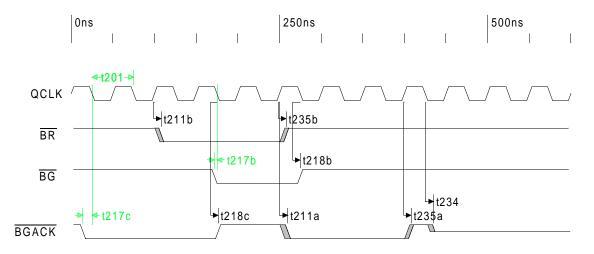

| Figure B.3 :  | QBus (QUICC) Arbitration App B-20                                 |

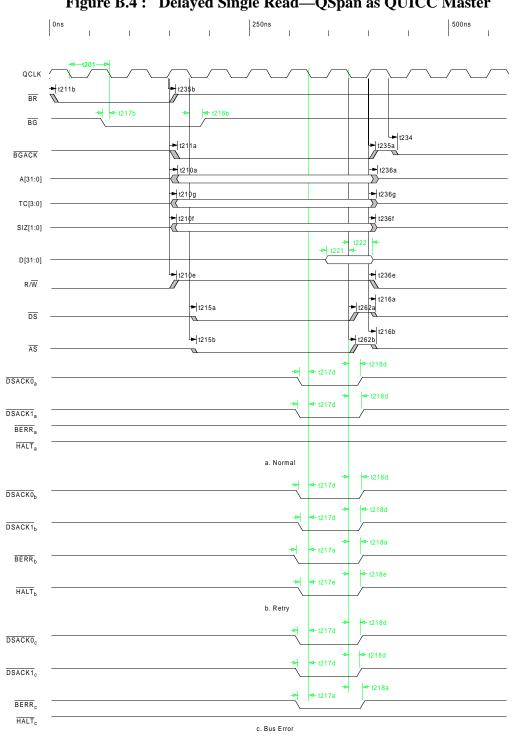

| Figure B.4 :  | Delayed Single Read—QSpan as QUICC Master App B-21                |

| Figure B.5 :  | Single Write - QSpan as QUICC Master App B-22                     |

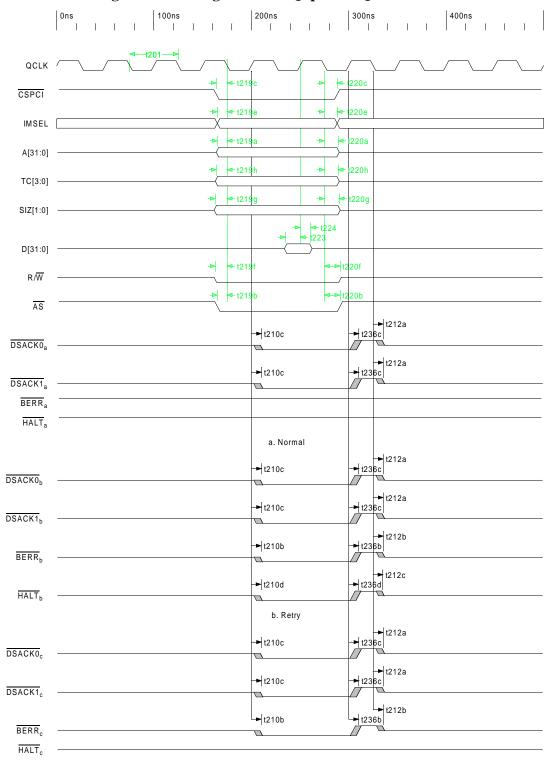

| Figure B.6 :  | Delayed Single Read—QSpan as QUICC Slave App B-23                 |

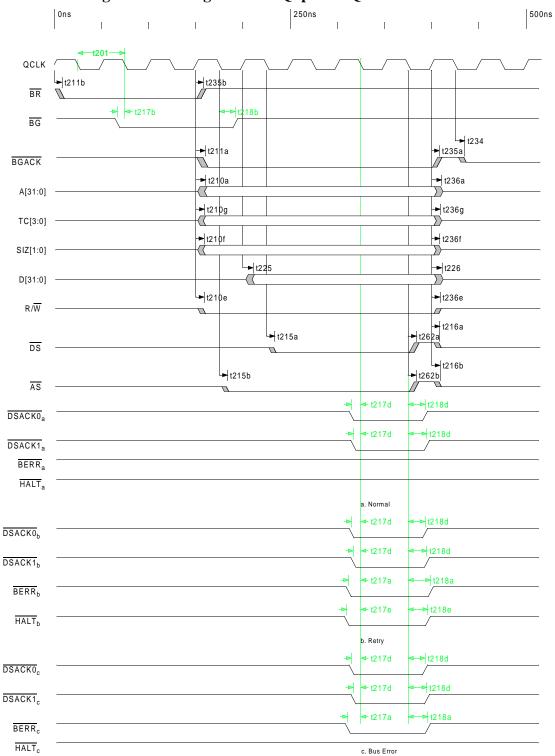

| Figure B.7 :  | Single Write - QSpan as QUICC Slave App B-24                      |

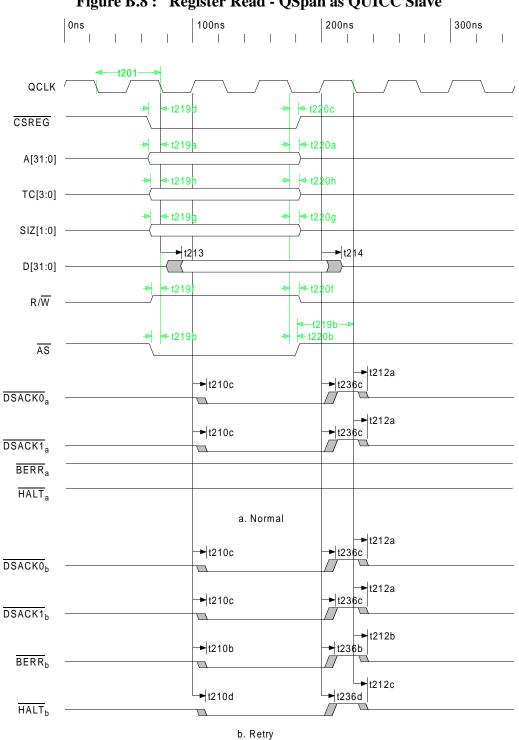

| Figure B.8 :  | Register Read - QSpan as QUICC Slave App B-25                     |

| Figure B.9 :  | Register Write - QSpan as QUICC Slave App B-26                    |

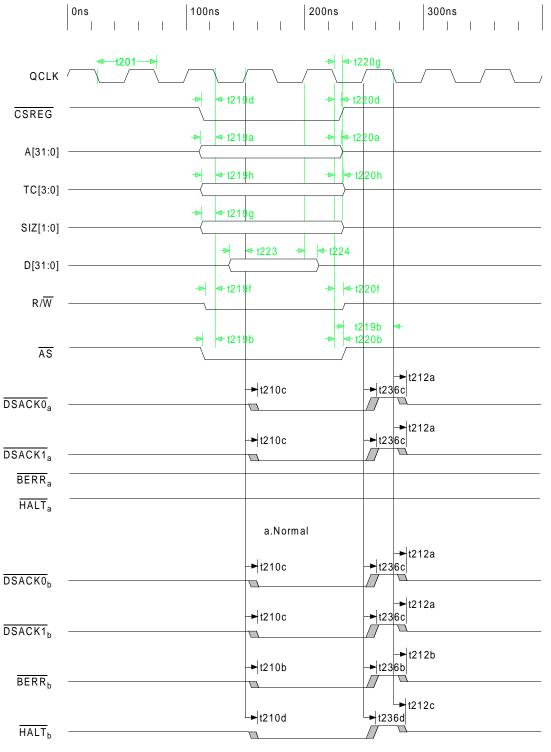

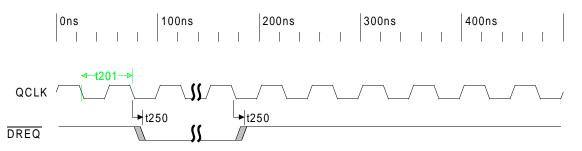

| Figure B.10 : | QUICC DREQ Timing App B-27                                        |

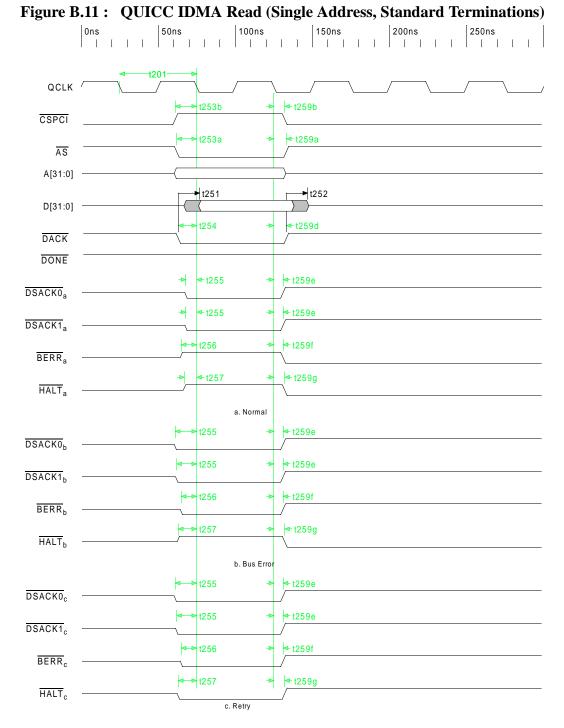

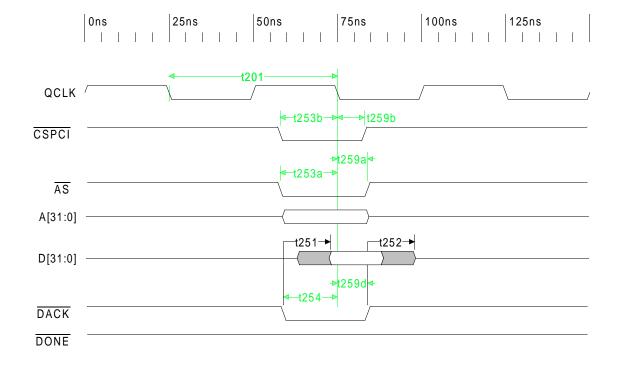

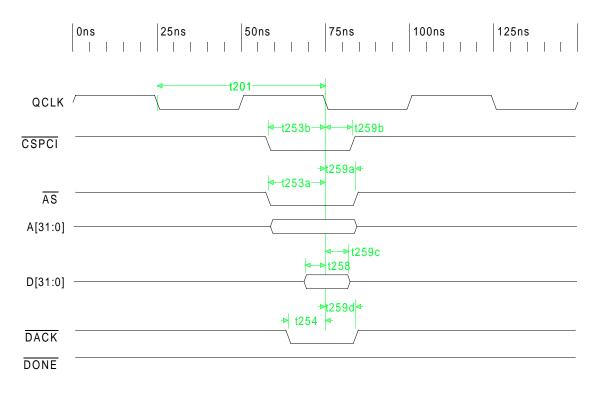

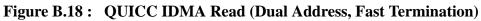

| Figure B.11 : | QUICC IDMA Read (Single Address, Standard Terminations) App B-28  |

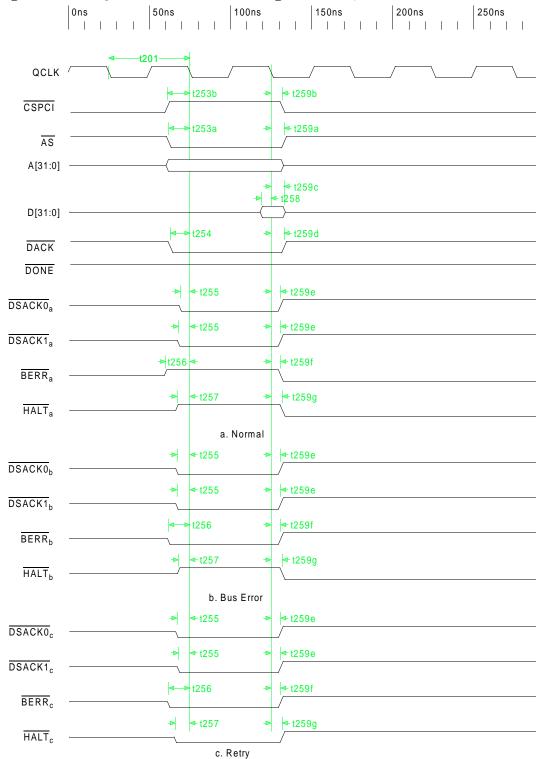

| Figure B.12 : | QUICC IDMA Write (Single Address, Standard Terminations) App B-29 |

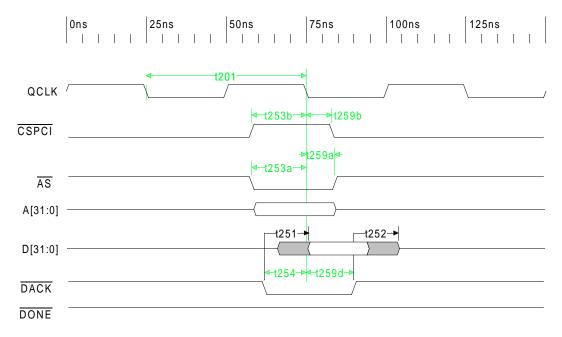

| Figure B.13 : | QUICC IDMA Read (Single Address, Fast Termination) App B-30       |

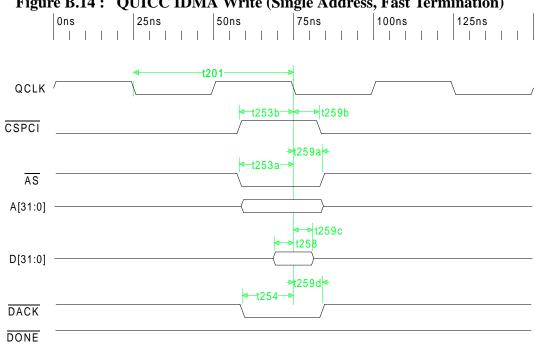

| Figure B.14 : | QUICC IDMA Write (Single Address, Fast Termination) App B-31      |

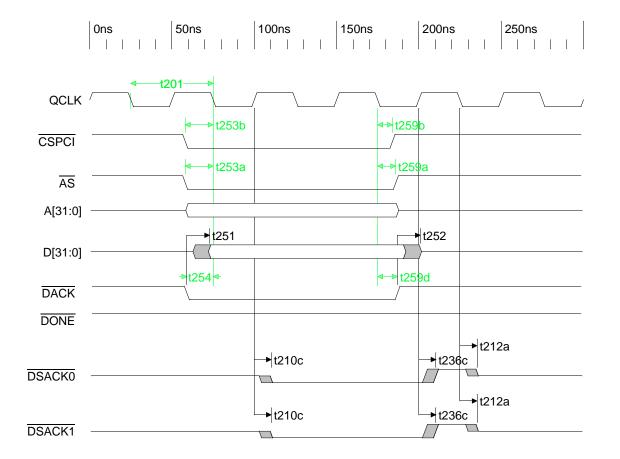

| Figure B.15 : | QUICC IDMA Read (Dual Address, Standard Termination) App B-32     |

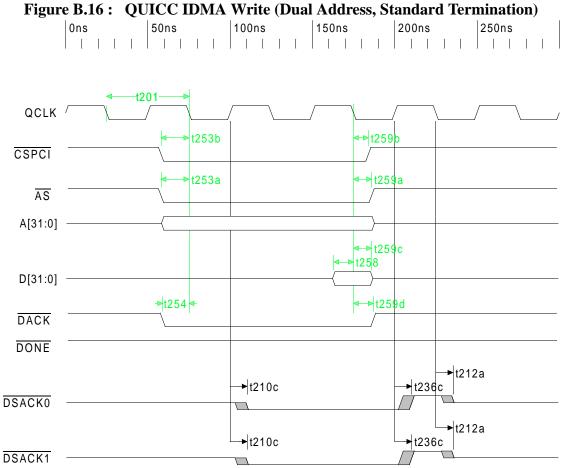

| Figure B.16 : | QUICC IDMA Write (Dual Address, Standard Termination) App B-33    |

| Figure B.17 : | QUICC IDMA Read (Dual Address, Fast Termination) App B-34         |

| Figure B.18 : | QUICC IDMA Read (Dual Address, Fast Termination)  | App B-35 |

|---------------|---------------------------------------------------|----------|

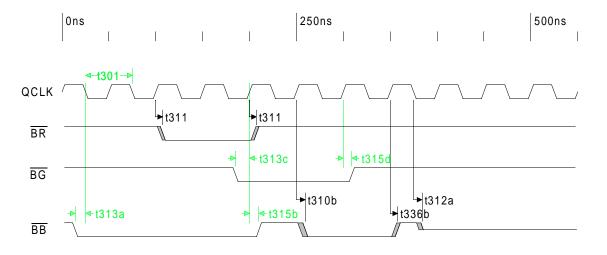

| Figure B.19 : | QBus (PowerQUICC) Arbitration                     | App B-36 |

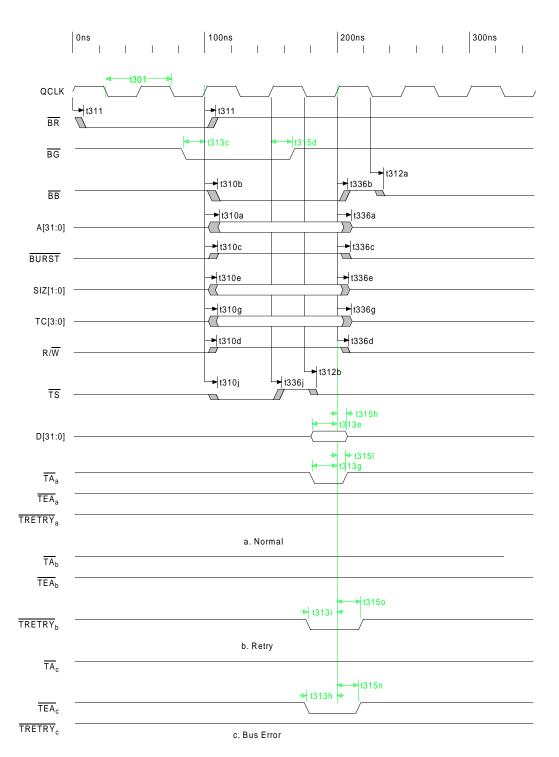

| Figure B.20 : | Single Read - QSpan as PowerQUICC Master          | App B-37 |

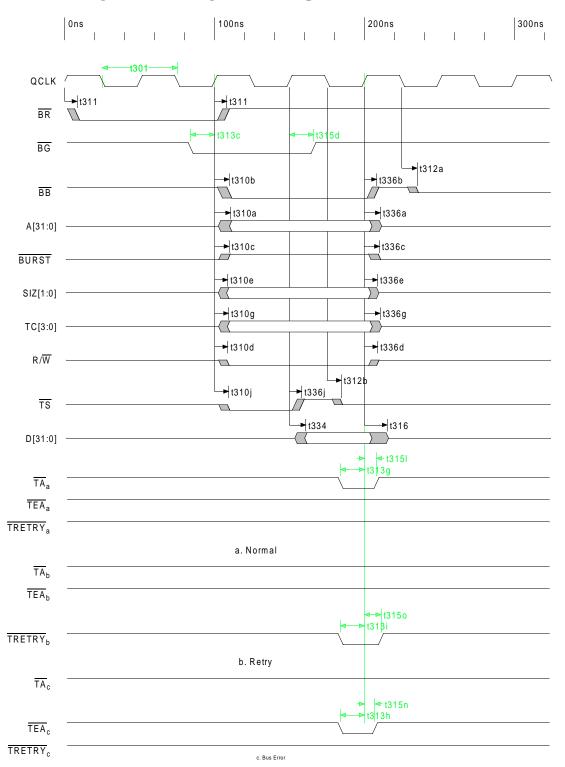

| Figure B.21 : | Single Write - QSpan as PowerQUICC Master         | App B-38 |

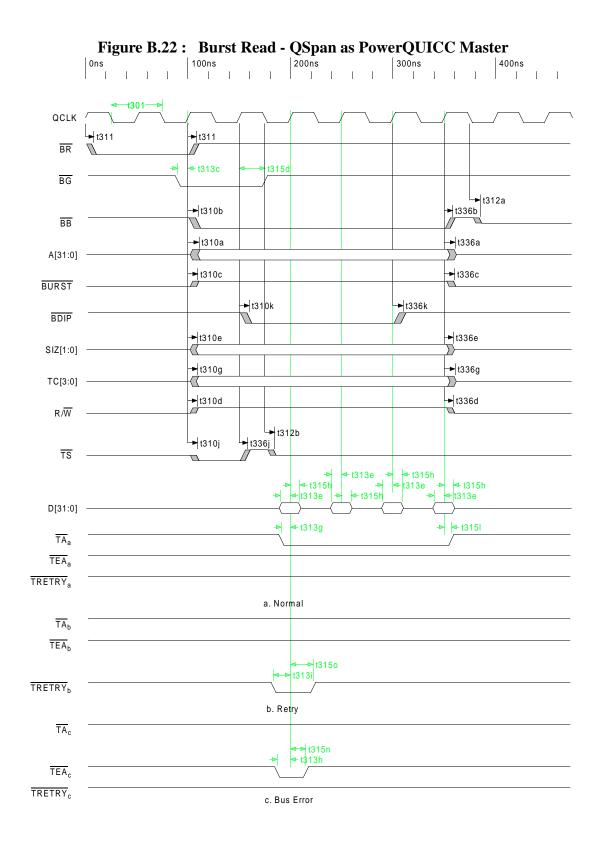

| Figure B.22 : | Burst Read - QSpan as PowerQUICC Master           | App B-39 |

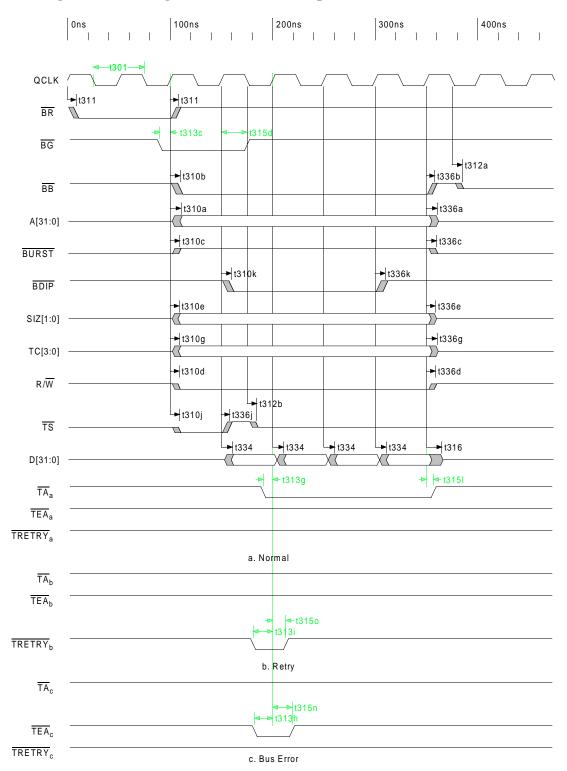

| Figure B.23 : | Aligned Burst Write - QSpan as PowerQUICC Master  | App B-40 |

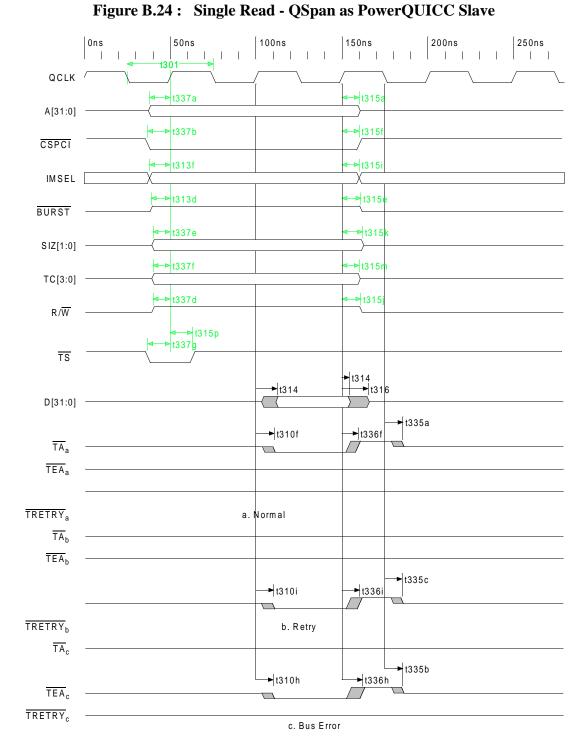

| Figure B.24 : | Single Read - QSpan as PowerQUICC Slave           | App B-41 |

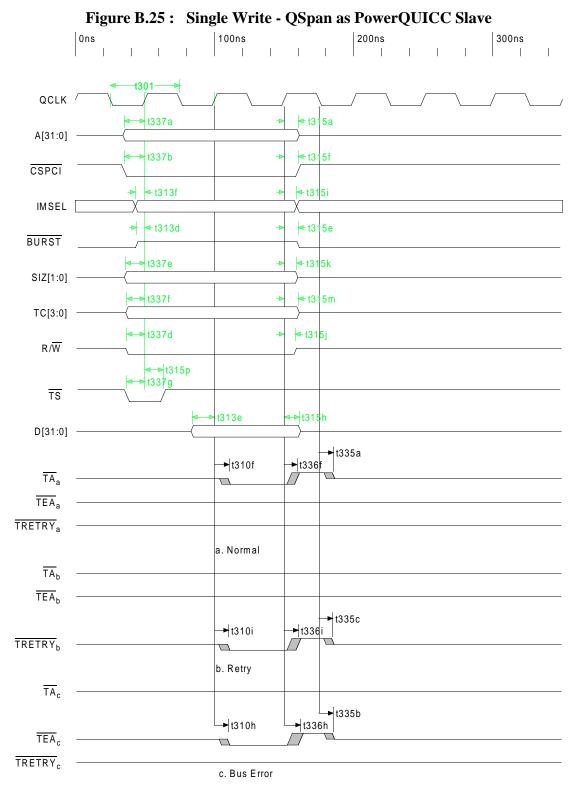

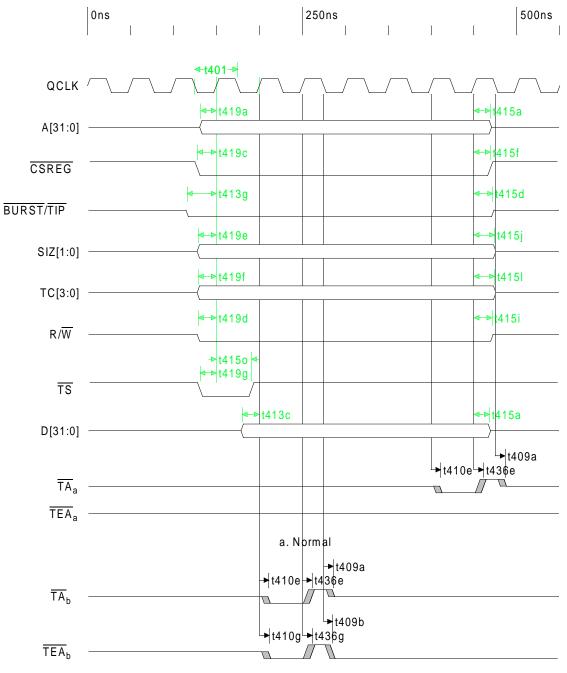

| Figure B.25 : | Single Write - QSpan as PowerQUICC Slave          | App B-42 |

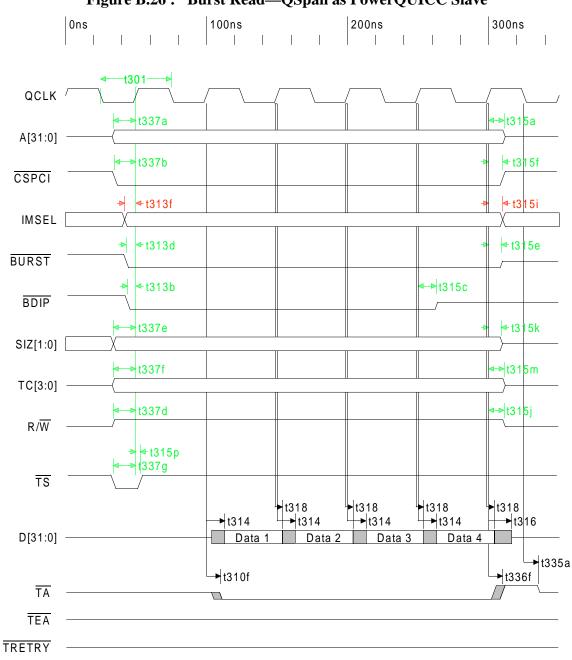

| Figure B.26 : | Burst Read—QSpan as PowerQUICC Slave              | App B-43 |

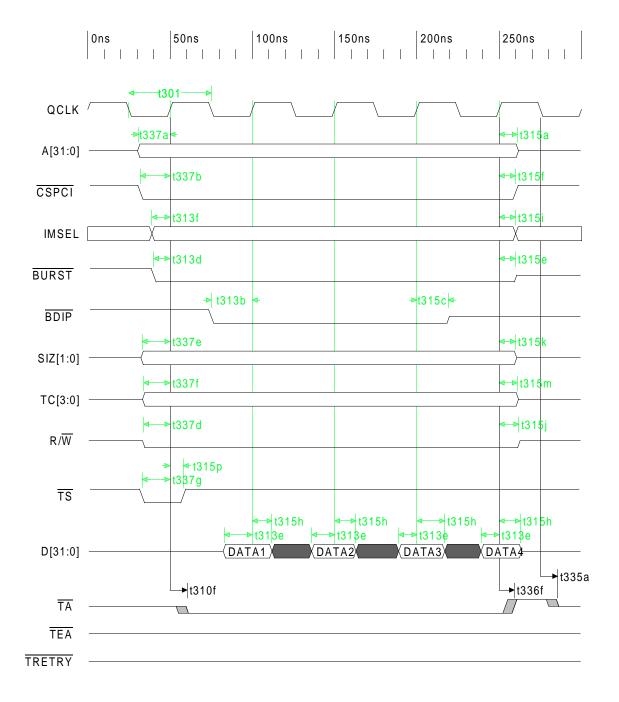

| Figure B.27 : | Burst Write—QSpan as PowerQUICC Slave             | App B-44 |

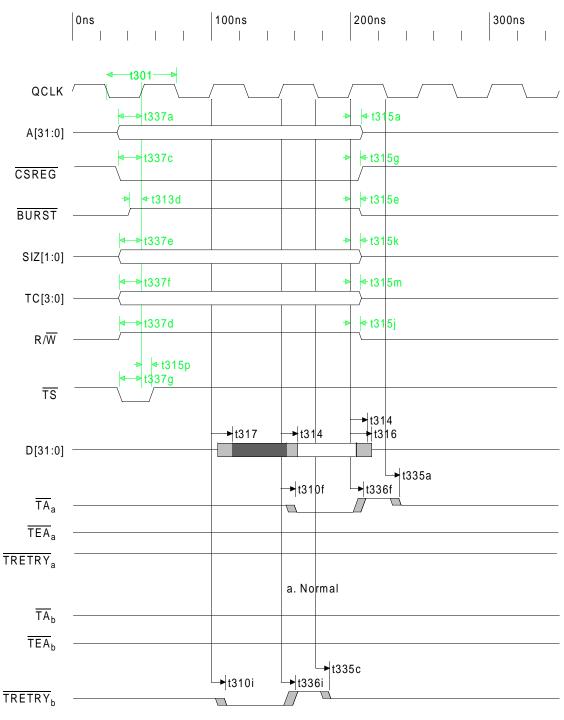

| Figure B.28 : | Register Read—QSpan as PowerQUICC Slave           | App B-45 |

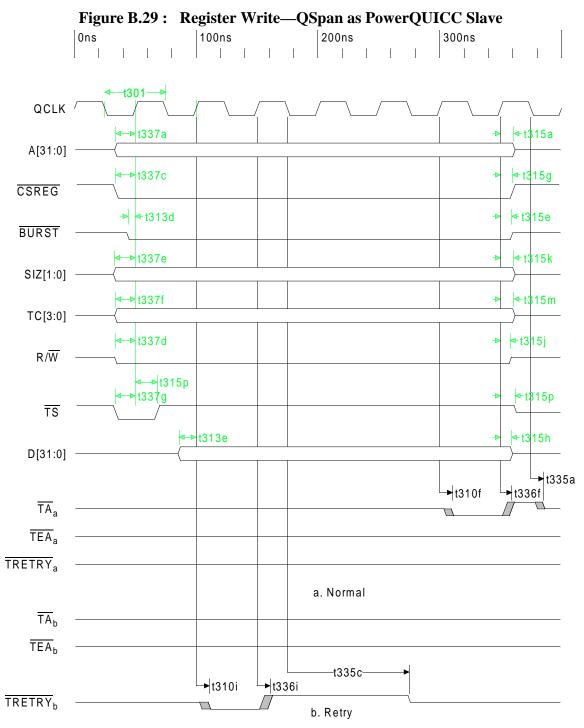

| Figure B.29 : | Register Write—QSpan as PowerQUICC Slave          | App B-46 |

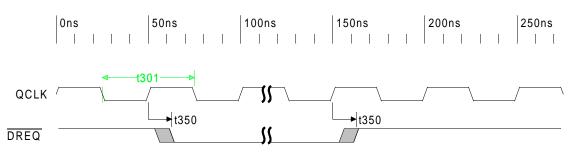

| Figure B.30 : | PowerQUICC DREQ Timing                            | App B-47 |

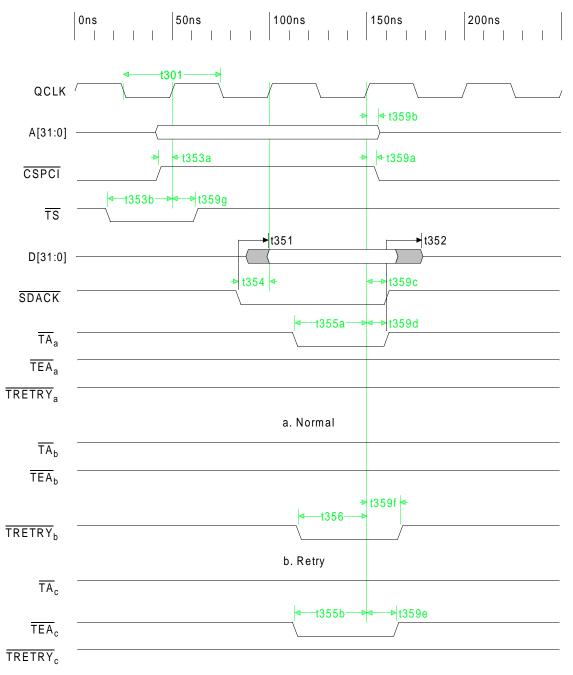

| Figure B.31 : | PowerQUICC IDMA Read (Single Address)             | App B-48 |

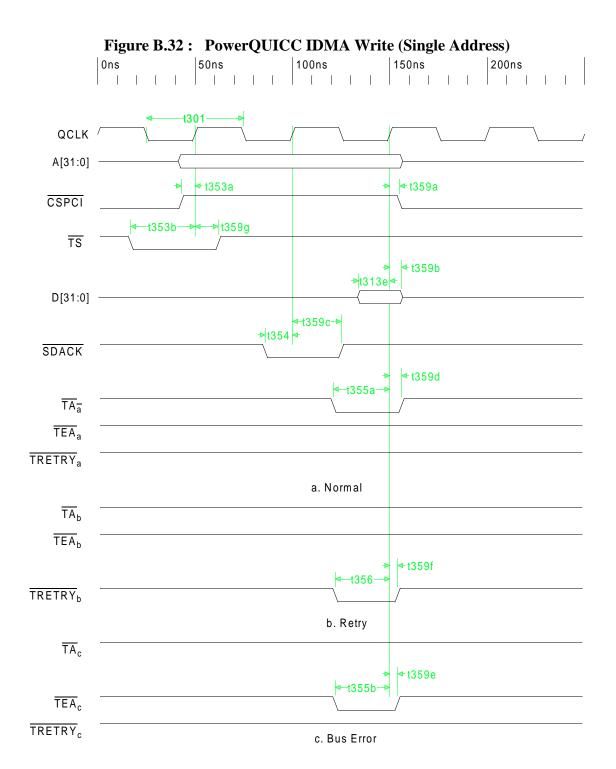

| Figure B.32 : | PowerQUICC IDMA Write (Single Address)            | App B-49 |

| Figure B.33 : | PowerQUICC IDMA Read (Dual Address)               | App B-50 |

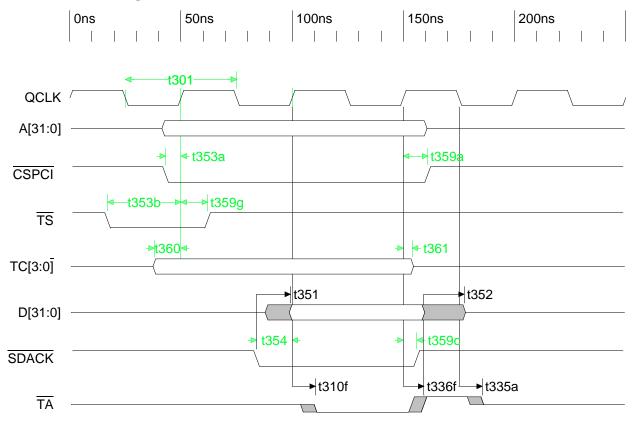

| Figure B.34 : | PowerQUICC IDMA Write (Dual Address)              | App B-51 |

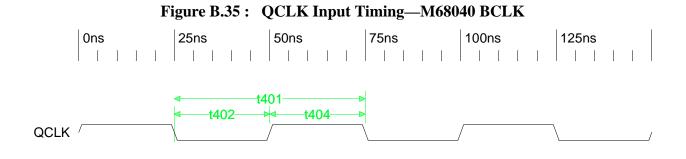

| Figure B.35 : | QCLK Input Timing—M68040 BCLK                     | App B-52 |

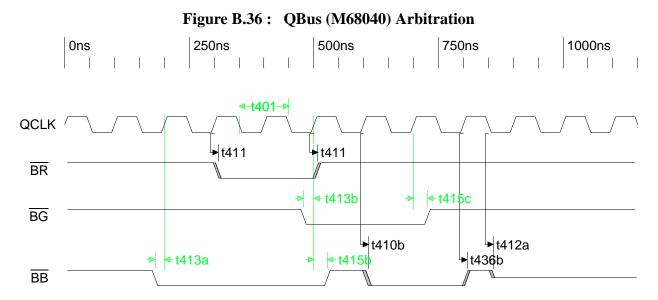

| Figure B.36 : | QBus (M68040) Arbitration                         | App B-52 |

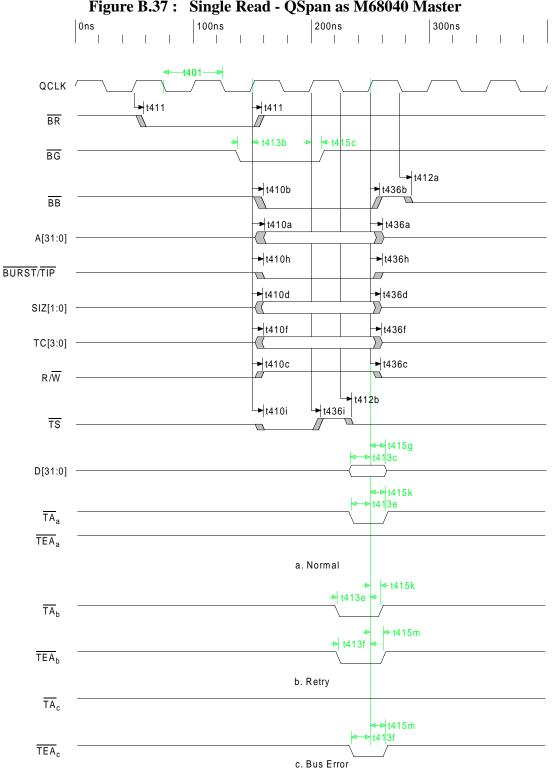

| Figure B.37 : | Single Read - QSpan as M68040 Master              | App B-53 |

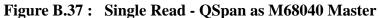

| Figure B.38 : | Single Read - QSpan as M68040 Master              | App B-54 |

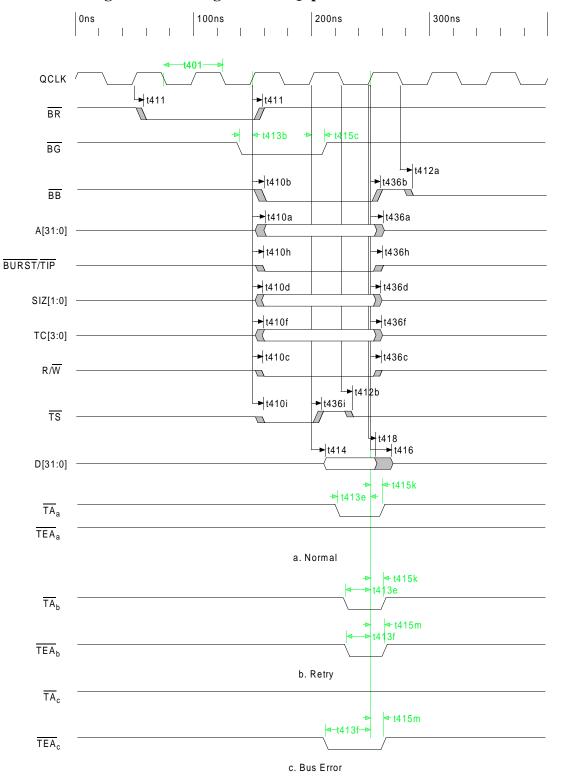

| Figure B.39 : | Single Read - QSpan as M68040 Slave               | App B-55 |

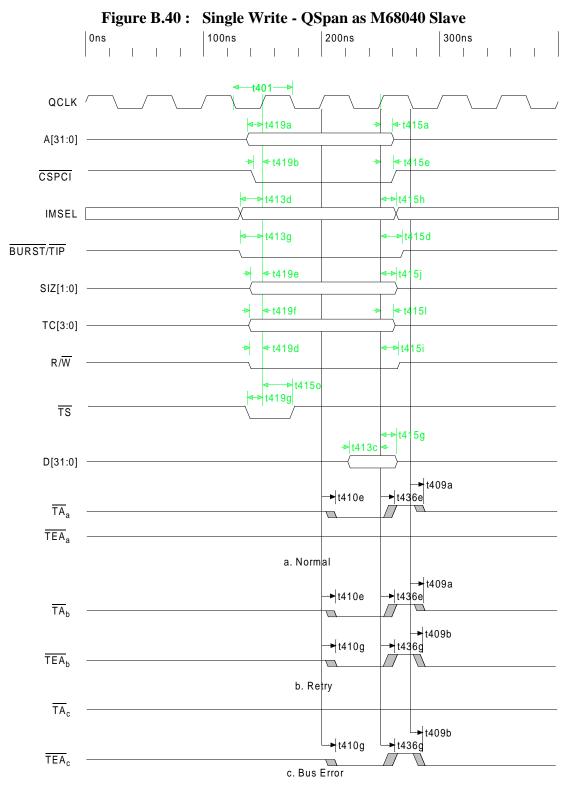

| Figure B.40 : | Single Write - QSpan as M68040 Slave              | App B-56 |

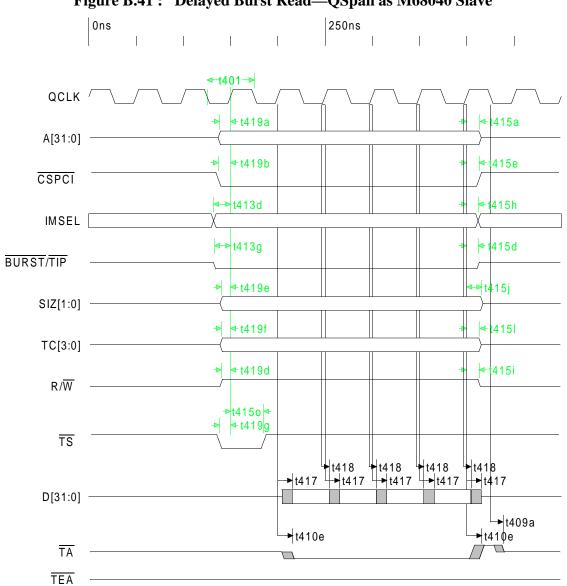

| Figure B.41 : | Delayed Burst Read—QSpan as M68040 Slave          | App B-57 |

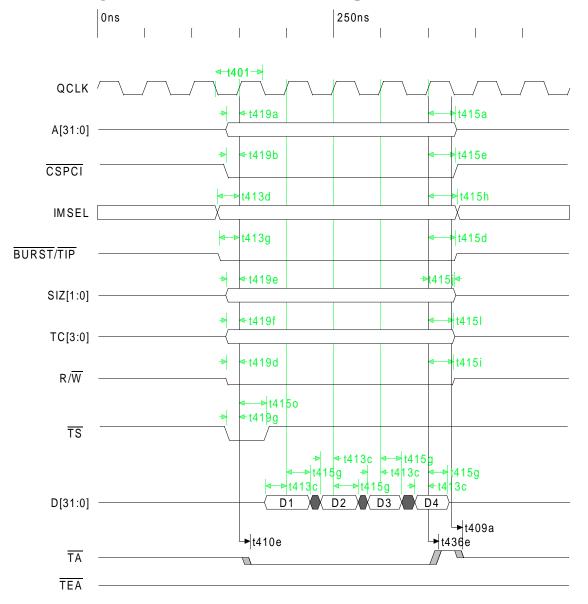

| Figure B.42 : | Posted Burst Write—QSpan as M68040 Slave          | App B-58 |

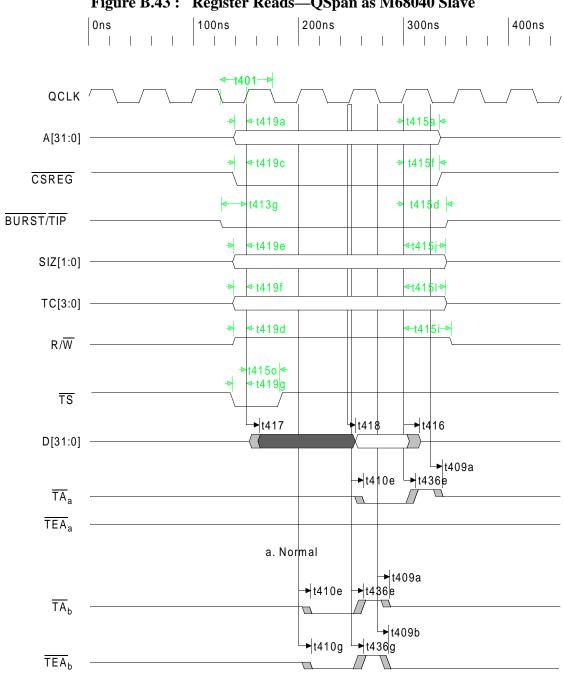

| Figure B.43 : | Register Reads—QSpan as M68040 Slave              | App B-59 |

| Figure B.44 : | Register Write—QSpan as M68040 Slave              | App B-60 |

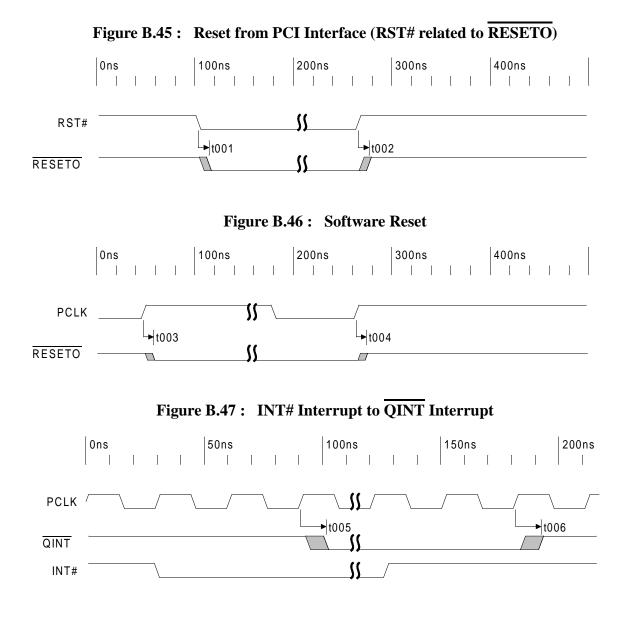

| Figure B.45 : | Reset from PCI Interface (RST# related to RESETO) | App B-61 |

| Figure B.46 : | Software Reset                                    | App B-61 |

| Figure B.47 : | INT# Interrupt to QINT Interrupt                  | App B-61 |

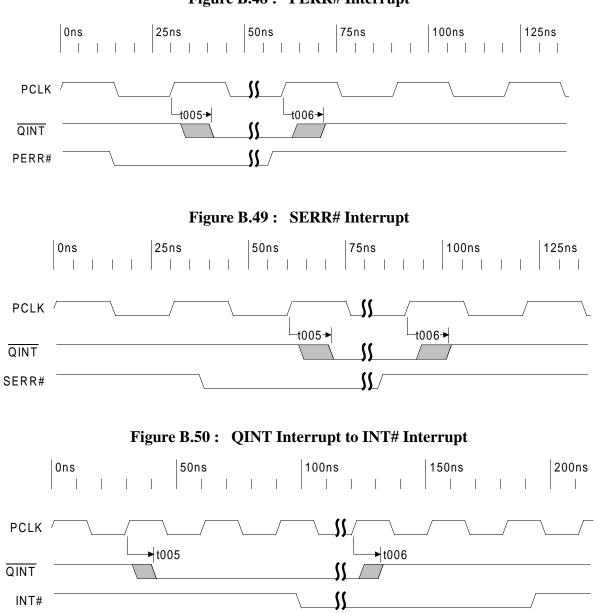

| Figure B.48 : | PERR# Interrupt                                   | App B-62 |

| Figure B.49 : | SERR# Interrupt                  | App B-62 |

|---------------|----------------------------------|----------|

| Figure B.50 : | QINT Interrupt to INT# Interrupt | App B-62 |

| Figure C.1 :  | QUICC Interface                  | App C-1  |

| Figure C.2 :  | PowerQUICC Interface             | Арр С-6  |

| Figure C.3 :  | M68040 Interface                 | App C-12 |

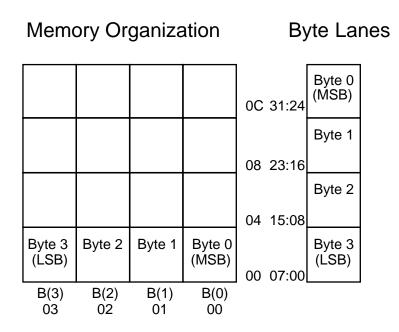

| Figure E.1 :  | Big-Endian System                | App E-1  |

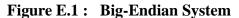

| Figure E.2 :  | Little-Endian System             | App E-2  |

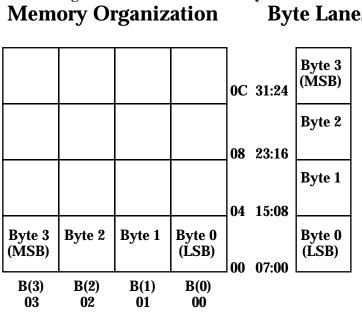

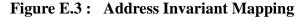

| Figure E.3 :  | Address Invariant Mapping        | App E-3  |

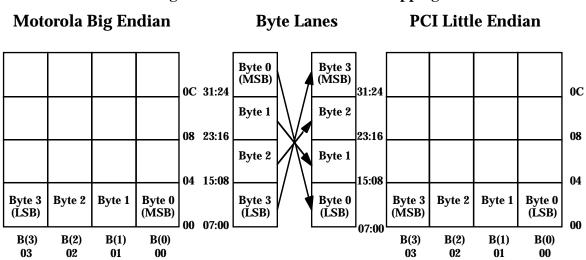

| Figure E.4 :  | Data Invariant Mapping           | App E-4  |

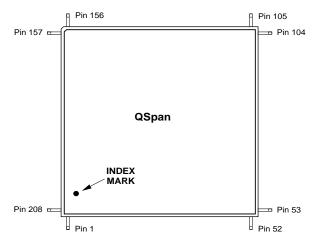

| Figure G.1 :  | 208-Pin PQFP                     | App G-2  |

| Figure G.1    | 208-Pin PQFP (continued)         | App G-3  |

| Figure G.2 :  | 256-lead PBGA                    | App G-4  |

| Figure G.2 :  | 256-lead PBGA (continued)        | App G-5  |

## **List of Tables**

| Table 1.1  | Signal Conventions Used in this document 1-4                         |

|------------|----------------------------------------------------------------------|

| Table 2.1  | Reset Options for QBus Slave Modes 2-7                               |

| Table 2.2  | Address Fields for QBus Slave Image 2-9                              |

| Table 2.3  | Control Fields for QBus Slave Image 2-9                              |

| Table 2.4  | Translation of QBus Address to PCI Address 2-13                      |

| Table 2.5  | Command Type Encoding for Transfer Type 2-14                         |

| Table 2.6  | Translation from QBus Transaction to PCI Transaction Type 2-14       |

| Table 2.7  | Little-Endian QBus Slave Channel Cycle Mapping 2-16                  |

| Table 2.8  | Big-Endian QBus Slave Channel Cycle Mapping 2-17                     |

| Table 2.9  | Translation of Cycle Termination from PCI Bus to QBus 2-21           |

| Table 2.10 | QUICC Cycle Terminations of QBus Slave Module 2-22                   |

| Table 2.11 | PowerQUICC Cycle Terminations of QBus Slave Module 2-22              |

| Table 2.12 | M68040 Cycle Terminations of QBus Slave Module 2-22                  |

| Table 2.13 | QBus Slave Channel Error Responses 2-23                              |

| Table 2.14 | Reset Options for QBus Master and Slave Modes 2-26                   |

| Table 2.15 | Address Fields for PCI Target Image 2-28                             |

| Table 2.16 | Control Fields for PCI Target Image 2-28                             |

| Table 2.17 | Translation of PCI Bus Address to QBus Address 2-31                  |

| Table 2.18 | Little-Endian PCI Target Write Cycle Mapping (32-Bit QBus Port) 2-34 |

| Table 2.19 | Big-Endian PCI Target Write Cycle Mapping (32-Bit QBus Port) 2-35    |

| Table 2.20 | Little-Endian PCI Target Read Cycle Mapping (32-Bit QBus Port) 2-36  |

| Table 2.21 | Big-Endian PCI Target Read Cycle Mapping (32-Bit QBus Port) 2-36     |

| Table 2.22 | Little-Endian PCI Target Read Cycle Mapping (16-Bit QBus Port) 2-37  |

| Table 2.23 | Big-Endian PCI Target Read Cycle Mapping (16-Bit QBus Port) 2-37     |

| Table 2.24 | Little-Endian PCI Target Read Cycle Mapping (8-Bit QBus Port) 2-38   |

| Table 2.25 | Big-Endian PCI Target Read Cycle Mapping (8-Bit QBus Port) 2-38      |

| Table 2.26 | QUICC Cycle Terminations of QBus Master Module 2-45                  |

| Table 2.27 | PowerQUICC Cycle Terminations of QBus Master Module 2-46             |

| Table 2.28 | M68040 Cycle Terminations of QBus Master Module                    | 2-46  |

|------------|--------------------------------------------------------------------|-------|

| Table 2.29 | Translation of Cycle Termination from QBus to PCI Bus              | 2-48  |

| Table 2.30 | The QSpan's Response to IDMA Errors                                | 2-54  |

| Table 2.31 | IDMA Interrupt Source, Enabling, Mapping, Status and Clear bits    | 2-55  |

| Table 2.32 | 16-Bit Little Endian IDMA Cycle Mapping                            | 2-56  |

| Table 2.33 | 16-Bit Big-Endian IDMA Cycle Mapping                               | 2-56  |

| Table 2.34 | 32-Bit Little-Endian IDMA Cycle Mapping                            | 2-57  |

| Table 2.35 | 32-Bit Big-Endian IDMA Cycle Mapping                               | 2-57  |

| Table 2.36 | PCI Memory Cycle Access to bits 15-08 of the PCI_CLASS register.   | 2-60  |

| Table 2.37 | Big-Endian QBus Access to bits 15-08 of the PCI_CLASS register     | 2-61  |

| Table 2.38 | Little-Endian QBus Access to bits 15-08 of the PCI_CLASS register. | 2-62  |

| Table 2.39 | PCI AD[31:16] lines asserted as a function of DEV_NUM field        | 2-63  |

| Table 2.40 | Mapping of Hardware-Initiated Interrupts                           | 2-66  |

| Table 2.41 | Interrupt Source, Enabling, Mapping, Status and Clear bits         | 2-67  |

| Table 2.42 | Software Interrupt Mapping, Status and Source bits                 | 2-68  |

| Table 2.43 | Destination of EEPROM Bits Read                                    | 2-71  |

| Table 2.44 | Hardware Reset Mechanisms                                          | 2-75  |

| Table 2.45 | Reset Options for QBus Master and Slave Modes                      | 2-77  |

| Table 2.46 | Test Mode Operation                                                | 2-78  |

| Table 3.1  | QBus Signal Names Compared to Motorola Signals                     | . 3-1 |

| Table 3.1  | Size Encoding for the SIZ[1:0] Signal                              | . 3-9 |

| Table 3.1  | Encoding for the SIZ[1:0] Signal                                   | 3-12  |

| Table 4.1  | PBGA Electrical Characteristics (non-PCI)                          | 4-2   |

| Table 4.2  | PBGA AC Electrical Characteristics (PCI Buffer)                    | . 4-3 |

| Table 4.3  | PBGA DC Electrical Characteristics (PCI Buffer)                    | . 4-3 |

| Table 4.4  | PQFP Device DC Electrical Characteristics (non-PCI)                | . 4-4 |

| Table 4.5  | PQFP Device AC Electrical Characteristics (PCI Buffer)             | 4-5   |

| Table 4.6  | PQFP Device DC Electrical Characteristics (PCI Buffer)             | 4-5   |

| Table 4.7  | Pin List for QSpan Signals                                         | 4-6   |

| Table 4.8  | PCI Bus Address/Data Pins                                          | 4-9   |

| Table 4.9  | QBus Address Pins                                                  | . 4-9 |

| Table 4.10 | QBus Data Pins 4-10                                             |

|------------|-----------------------------------------------------------------|

| Table 4.11 | Pin Assignments for Power (V <sub>DD</sub> ) 4-10               |

| Table 4.12 | Pin Assignments for Ground (V <sub>SS</sub> ) 4-11              |

| Table 4.13 | No Connect Pin Assignments 4-11                                 |

| Table 4.14 | Pin-Out of QSpan 256-PBGA 4-12                                  |

| Table 4.15 | Pin-Out of QSpan 208-Pin PQFP 4-13                              |

| Table A.1  | Register Map App A-2                                            |

| Table A.2  | PCI Configuration Space ID Register App A-4                     |

| Table A.3  | PCI Configuration Space Control and Status Register App A-5     |

| Table A.4  | PCI Configuration Class Register App A-7                        |

| Table A.5  | PCI Configuration Miscellaneous 0 Register App A-8              |

| Table A.6  | PCI Configuration Base Address for Memory Register App A-9      |

| Table A.7  | PCI Configuration Base Address for Target 0 Register App A-10   |

| Table A.8  | PCI Address Lines Compared as a Function of Block Size App A-11 |

| Table A.9  | PCI Configuration Base Address for Target 1 Register App A-12   |

| Table A.10 | PCI Address Lines Compared as a Function of Block Size App A-13 |

| Table A.11 | PCI Configuration Subsystem ID Register App A-14                |

| Table A.12 | PCI Configuration Expansion ROM Base Address Register App A-15  |

| Table A.13 | Writable BA bits as a function of Block Size App A-16           |

| Table A.14 | PCI Configuration Miscellaneous 1 Register App A-17             |

| Table A.15 | PCI Bus Target Image 0 Control Register App A-18                |

| Table A.16 | PCI Bus Target Image 0 Address Register App A-20                |

| Table A.17 | PCI Address Lines Compared as a Function of Block Size App A-20 |

| Table A.18 | PCI Bus Target Image 1 Control Register App A-22                |

| Table A.19 | PCI Bus Target Image 1 Address Register App A-24                |

| Table A.20 | PCI Address Lines Compared as a Function of Block Size App A-24 |

| Table A.21 | PCI Bus Expansion ROM Control Register App A-26                 |

| Table A.22 | PCI Bus Error Log Control and Status Register App A-27          |

| Table A.23 | PCI Bus Address Error Log Register App A-28                     |

| Table A.24 | PCI Bus Data Error Log Register App A-29                        |

| Table A.25 | IDMA Control and Status Register App A-30                       |

| T-11- A 26 |                                                                      |

|------------|----------------------------------------------------------------------|

| Table A.26 | IDMA Address Register App A-33                                       |

| Table A.27 | IDMA Transfer Count Register App A-34                                |

| Table A.28 | Configuration Address Register App A-35                              |

| Table A.29 | PCI AD[31:16] lines asserted as a function of DEV_NUM field App A-36 |

| Table A.30 | Configuration Data Register App A-37                                 |

| Table A.31 | IACK Cycle Generator Register App A-38                               |

| Table A.32 | Interrupt Status Register App A-39                                   |

| Table A.33 | Interrupt Control Register App A-41                                  |

| Table A.34 | Interrupt Direction Register App A-43                                |

| Table A.35 | Interrupt Control Register 2 App A-45                                |

| Table A.36 | Miscellaneous Control and Status Register App A-46                   |

| Table A.37 | Master/Slave Mode (MSTSLV field) App A-48                            |

| Table A.38 | EEPROM Control and Status Register App A-49                          |

| Table A.39 | QBus Slave Image 0 Control Register App A-50                         |

| Table A.40 | QSpan Response to Single Cycle Access App A-50                       |

| Table A.41 | QSpan Response to Burst Cycle Access App A-51                        |

| Table A.42 | QBus Slave Image 0 Address Translation Register App A-52             |

| Table A.43 | Address Lines Translated as a Function of Block Size App A-52        |

| Table A.44 | QBus Slave Image 1 Control Register App A-53                         |

| Table A.45 | QSpan Response to Single Cycle Access (BURST negated) App A-53       |

| Table A.46 | QSpan Response to Burst Cycle Access (BURST asserted) App A-54       |

| Table A.47 | QBus Slave Image 1 Address Translation Register App A-55             |

| Table A.48 | QBus Address Lines Compared as a function of Block Size App A-55     |

| Table A.49 | QBus Error Log Control and Status Register App A-56                  |

| Table A.50 | QBus Address Error Log App A-57                                      |

| Table A.51 | QBus Data Error Log App A-58                                         |

| Table B.1  | Timing Parameters for QUICC Interface App B-2                        |

| Table B.2  | Timing Parameters for PowerQUICC Interface (3.3 volt, PBGA). App B-8 |

| Table B.3  | Timing Parameters for PowerQUICC Interface (5 volt, PQFP) App B-12   |

| Table B.4  | Timing Parameters for M68040 Interface App B-16                      |

| Table B.5  | Timing Parameters for Interrupts and Resets App B-18                 |

|            | - **                                                                 |

| Table B.6 | Timing Parameters for Reset Options App B-18                      |

|-----------|-------------------------------------------------------------------|

| Table B.7 | Direction of QBus Signals During QUICC IDMA Cycles App B-27       |

| Table B.8 | Direction of QBus Signals During PowerQUICC IDMA Cycles. App B-47 |

| Table D.1 | Summary of the QSpan's Miscellaneous Control Register App D-2     |

| Table D.2 | QBus Slave Channel Programming Summary App D-2                    |

| Table D.3 | Register Access App D-3                                           |

| Table D.4 | PCI Target Image Programming Summary App D-3                      |

| Table D.5 | QBus Error Logging Programming Summary App D-5                    |

| Table D.6 | IDMA Channel Programming Summary App D-5                          |

| Table D.7 | IDMA Channel Interrupt Programming Summary App D-6                |

| Table D.8 | PCI Configuration Cycle Programming Summary App D-7               |

| Table D.9 | PCI Expansion ROM programming App D-8                             |

| Table F.1 | Power Dissipation App F-1                                         |

| Table F.2 | 5.0V Absolute Maximum Ratings App F-1                             |

| Table F.3 | 5.0V Recommended Operating Conditions App F-2                     |

| Table F.4 | 5.0 Volt Package Thermal Resistance App F-2                       |

| Table F.5 | Power Dissipation App F-3                                         |

| Table F.6 | 3.3 Volt Absolute Maximum Ratings App F-3                         |

| Table F.7 | 3.3 Volt Recommended Operating Conditions App F-3                 |

| Table F.8 | 3.3 Volt Package Thermal Resistance App F-4                       |

| Table G.1 | Standard Ordering Information App G-6                             |

## **Corporate Profile**

Tundra Semiconductor Corporation is an international, fabless semiconductor company focused on the design, development and support of bus-bridging semiconductors for embedded datacommunications and telecommunications applications.

Our mission is to provide high-quality components that enable embedded systems designers to get to market faster with a more competitive product. Tundra takes a 'total product solution' approach to its bus-bridges. This approach includes the QSpan Reference Design Kit (RDK) and the QSpan Software Development Kit (SDK). In addition, customers are supported by our acclaimed applications engineering support.

Tundra offers a growing line of PCI Bus bus-bridging chips that support embedded processors, such as the QSpan, the Motorola© embedded processor-to-PCI bridge. Our components are developed through strategic partnerships with leading processor manufacturers such as Motorola.

We also have an industry-leading family of VMEbus bus-bridging components, including the Universe II, the first commercially available VME-to-PCI Bus bridge, and the SCV64, the pioneering VME64 interface device.

Tundra develops devices that bridge leading bus types to industry-leading processors in the fast-growing embedded systems market. We accomplish this in two ways. First, we form strategic relationships with leading manufacturers. Next, we utilize a Lead Customer model, in which we invite innovators in embedded systems design to help further define the functionality of a Tundra component.

Tundra Semiconductor Corporation

603 March Road, Kanata, Ontario, Canada K2K 2M5 TEL (613) 592-0714 1-800-267-7231 FAX (613) 592-1320 http://www.tundra.com QSpan<sup>™</sup> PCI to Motorola Processor Bridge Manual

## **1** General Information

### **1.1 Introduction**

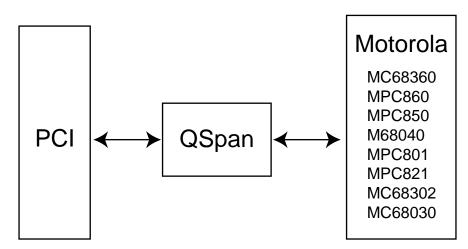

The QSpan<sup>TM</sup> chip is a member of Tundra Semiconductor Corporation's growing family of PCI bus-bridging devices enabling board designers to bring PCI-based embedded products to market faster, for less cost and with high performance. Developed as part of an ongoing strategic relationship with Motorola®, the QSpan is a PCI to processor bus bridge. The QSpan is designed to gluelessly bridge the QUICC<sup>TM</sup> (MC68360), the PowerQUICC<sup>TM</sup> (MPC860, MPC850, MPC801), the M68040, the M68060 and the MPC821 embedded controllers to PCI. The QSpan can also be connected to lower end communications controller and processors such as the MC68302 and MC68030, with some additional glue logic.

Figure 1.1 The QSpan Bridging PCI and Processor Buses

### **1.2 Product Overview**

#### **The Features**

The QSpan has the following features:

- A direct connect interface to the PCI bus for Motorola's QUICC (MC68360), PowerQUICC (MPC860, MPC850, MPC801), the M68040, the M68060 and the MPC821 embedded controllers

- Support for up to 50 MHz MPC8xx bus frequencies

- Available in 208-PQFP (5 volt) and 256-PBGA (3.3 volt)

- 32-bit PCI interface compliant with PCI Revision 2.1

- Five FIFOs buffer multiple transactions in both directions

- Accepts and generates burst reads and writes on PCI and processor buses

- Separate channel supports QUICC and PowerQUICC IDMA

- Flexible address space mapping and translation between the PCI and processor buses;

- Programmable endian byte ordering

- Four user programmable images

- Serial EEPROM interface for Plug'N Play compatibility

- Interrupt handler and generator on PCI bus and processor bus

- Registers accessible from both PCI and processor buses

- PCI bus and processor bus can be operated at different clock frequencies

- IEEE 1149.1 JTAG boundary-scan support

### **1.3 Using This Document**

This manual is organized as follows:

- Chapter 1 General Information

- Chapter 2 Functional Description

- Chapter 3 Signal Description

- Chapter 4 Signals and DC Characteristics

- Appendix A Registers

- Appendix B Timing

- Appendix C Typical Applications

- Appendix D Initialization

- Appendix E Endian Mapping

- Appendix F Operating and Storage Conditions

- Appendix G Mechanical and Ordering Information

- Index

- Sales Network

Chapter 1 introduces the QSpan and provides the reader with conventions used in the manual.

Chapter 2 describes the QSpan's functionality.

Chapter 3 describes the QSpan's signals.

Chapter 4 provides the DC characteristics and pin-out.

The Appendices are reference sources necessary for the implementation of the QSpan.

The Sales Network appendix at the end of the manual lists our current team of national and international sales representatives and distributors.

## **1.4 Revision History**

The current version of the *QSpan - PCI to Motorola Processor Bridge Manual*, document number 8091860.MD302.05, is a revision of document 8091860.MD302.04.

All of the chapters for this manual have been updated. However, the main revisions in the new manual are:

- Chapter 2 Functional Description

- Chapter 4 Signals and DC Characteristics

- Appendix B Timing

## **1.5** Conventions

#### 1.5.1 Signals

Signals on the QSpan are either active high or active low. Active low signals are defined as true (asserted) when they are at a logic low. Similarly, active high signals are defined as true at a logic high. Signals are considered asserted when active and negated when inactive, irrespective of voltage levels.

For voltage levels, the use of '0' indicates a low voltage while a '1' indicates a high voltage.

Table 1.1

Signal Conventions Used in this document

| SIGNAL# | active low signals on the PCI interface  |

|---------|------------------------------------------|

| SIGNAL  | active low signals on the QBus interface |

In addition to the difference between PCI and processor bus signals, the PowerQUICC conventions are different from both the other Motorola conventions and the PCI conventions. PowerQUICC signals are arranged in the opposite order from the other processor buses and PCI buses: i.e., the least significant signals are listed first. For example, the QUICC A[31:0] signals correspond to the PowerQUICC A[0:31] signal. This manual adopts the convention that the most significant bit (address or data) is always the largest number. PowerQUICC designers must ensure that they connect their pins accordingly: e.g., pin A[31] on the QSpan connects to pin A[31] on the QUICC bus, but connects to pin A[0] on the PowerQUICC bus. This applies to all PowerQUICC buses (D[31:0], AT[3:0], TSIZ[1:0]) not only the address bus.

#### 1.5.2 Terminology

The term "QBus" is used as a generic term referring to the interface between the QSpan and the processor bus to which the QSpan is connected.

When discussing bus ownership, this manual uses "master" to indicate the bus owner, and "slave" or "target" to indicate the address accessed by the master. The term "master" is used for both the PCI and the QBus, while "slave" is reserved for addresses accessed by QBus masters, and "target" is reserved for addresses accessed by PCI masters.

Note also that the term "cycle" refers to a single data beat, while a "transaction" is composed of one or more cycles.

#### 1.5.3 Symbols

Caution: This symbol alerts the reader to procedures or operating levels which may result in misuse of or damage to the QSpan.

Note: This symbol directs the reader's attention to useful information or suggestions.

The globe symbol alerts the reader that the initialization must be performed as a minimum to access the channel in question.

### **1.6 QSpan Technical Support and Documentation**

Tundra is dedicated to providing our customers with superior technical documentation and support. The following means of support are available:

- 1. **The QSpan User Manual.** This is the main source of technical information. We strive hard to produce excellent documentation, and this manual contains the answers to most of our customers' questions.

- 2. **The QSpan Documentation Web Page**. This contains the latest manual, application notes, FAQ, articles, and any device errata and manual addenda. Please visit and bookmark http://www.tundra.com

- **3. QSpan Design Notes**. This documentation informs and guides clients through specific design issues associated with the QSpan. The latest Design Notes are available on the Tundra website www.tundra.com.

$<sup>\</sup>bigotimes$

- 4. **The Designer's Resource Forum**. This is a public discussion forum at http://www.tundra.com which allows you to post questions and read threads pertaining specifically to the QSpan. Tundra technical support staff moderate this forum and promptly respond to customer inquiries.

- 5. **The Designer's Resource Center.** You can tailor how the Tundra web site is presented to you by using this web resource, available from http://www.tundra.com. There, you may also register to receive automatic e-mail notification when the addendum, manual, or any other "resource" has changed. This is the best way to ensure that you always have the latest QSpan documentation.

- 6. **support**@**tundra.com**. You may also direct questions and feedback to Tundra using this e-mail address. Please include "QSpan" in the subject header of your message.

- 7. **Phone support.** Tundra's technical support staff may be reached at (613) 592-0714 Please ask for QSpan technical support.

## 2 Functional Description

This chapter explains the operation of the QSpan. It is organized in terms of the data and control paths of the QSpan. The following topics are discussed.

- "The QBus Slave Channel" on page 2-5

- "The PCI Target Channel" on page 2-24

- "The IDMA Channel" on page 2-49

- "The Register Channel" on page 2-58

- "The Interrupt Channel" on page 2-64

- "The EEPROM Channel" on page 2-69

- "Reset Options" on page 2-75

- "Hardware Implementation Issues" on page 2-78

### 2.1 Architectural Overview

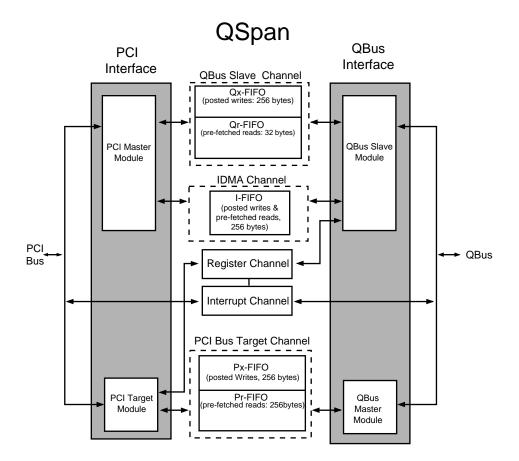

The QSpan has two interfaces, a PCI bus interface and a "QBus" Interface (see Figure 2.1). The QBus is used to denote the programmable 860/360 and 040 interface on the QSpan. The PCI Interface is the QSpan's connection to the PCI bus. The PCI Interface contains a PCI Master Module and a PCI Target Module. The QBus Interface is the interface which connects the QSpan to the processor bus. The processor interface also supports master and slave transactions. The QBus may be directly connected to a QUICC bus, a PowerQUICC bus, and/or a M68040 bus (or some other bus with glue logic). Each of the two interfaces has two functionally distinct modules: a master module, and a slave (or target) module. These modules are connected to the different functional channels operating in the QSpan.

The rest of this section describes the QSpan in terms of its channels.

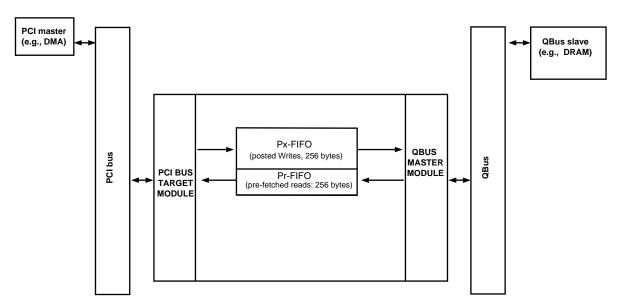

Figure 2.1 QSpan Functional Block Diagram

#### 2.1.1 The QBus Slave Channel: From Processor to PCI Bus

PCI Memory and I/O spaces are accessible through two slave images associated with the QBus Slave Channel. (Configuration space is accessible by accessing the CON\_DATA register, page A-37). The QBus slave images are selected using a pair of chip-select signals on the QSpan.

The QBus Slave Channel supports posted writes, and delayed single reads and writes. Write transactions from the QBus to the PCI bus can be posted or delayed. Posted writes are queued in the Qx-FIFO with immediate data acknowledgment on the QBus. The QSpan then completes the write on the PCI bus. Delayed transactions - both reads and writes - require data acknowledgment on the PCI bus before data acknowledgment is provided on the QBus.

#### 2.1.2 The PCI Target Channel: From PCI Bus to QBus

The QSpan provides two programmable target images on the PCI Interface. These images can be mapped anywhere in Memory or I/O space. Transactions from the PCI bus to the QBus can be executed as delayed or posted transactions.

PCI burst writes can be posted to ensure zero-wait state bursting. The 256-byte write FIFO (the Px-FIFO) allows for long PCI burst writes to be queued.

Delayed writes and reads must complete on the processor bus before data acknowledgment occurs on the on the PCI bus. Reads are always executed as delayed transactions, but the QSpan can be configured to pre-fetch read data. This supports long read bursts on the PCI bus. Pre-fetched reads are queued in a 256-byte FIFO (the Pr-FIFO).

#### 2.1.3 The IDMA Channel

The QSpan can be programmed to operate as a QBus IDMA peripheral for high performance data transfer between the QBus and the PCI bus. For transfers going to or from PCI, software can perform bulk data movement using only the IDMA and the QSpan. The IDMA channel supports single and dual address cycles, and fast-terminations. A separate set of IDMA handshake signals are provided on the QBus. The IDMA Channel can be used by external QBus masters to read data from or write data to a PCI target in one direction at a time. The IDMA Channel contains a 256-byte FIFO (the I-FIFO) and a set of IDMA registers (see page A-30 to page A-34).

When programmed to perform writes to the PCI bus, the QSpan requests transfers from the processor IDMA on the QBus. Once the processor's IDMA is requested for write data, it loads posted writes into the I-FIFO. When enough data is available in the I-FIFO for a burst transaction on the PCI bus, the QSpan requests the PCI bus and begins bursting data to the PCI target. This continues until the number of transfers programmed in the QSpan's IDMA\_CS register completes. This technique provides high data throughput by using the IDMA to drive data transfers across the QBus.

When programmed to perform IDMA transfers from the PCI bus to the QBus, the QSpan reads data from a PCI target and loads the data into the I-FIFO. As the I-FIFO begins to fill, the QSpan requests the processor's IDMA to transfer data from the QSpan to the destination on the QBus. The processor's IDMA then transfers data from the QSpan's I-FIFO until the number of transfers programmed into the QSpan's IDMA registers completes or the QSpan signals to the processor's IDMA that there is currently no further data available in the I-FIFO. Like the method used for PCI writes, this technique optimizes data transfer by taking full advantage of the processor's IDMA. See "The IDMA Channel" on page 2-49.

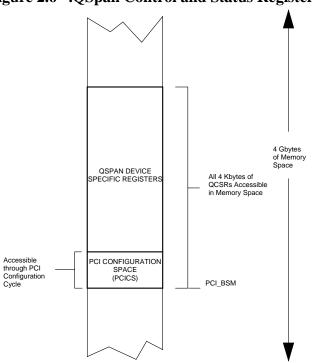

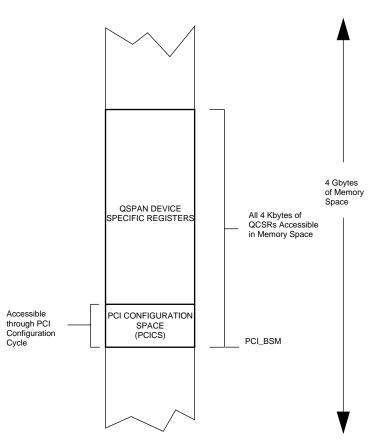

#### 2.1.4 The Register Channel

The QSpan provides 4 Kbytes of Control and Status Registers (QCSRs) that are used to program PCI settings as well as the QSpan's device specific parameters. All of the QCSR space is accessible from both the PCI bus and the QBus.

An internal arbitration mechanism is used to grant access to the QCSRs. The access mechanisms (including arbitration protocol) for the QCSRs differ depending on whether the registers are accessed from the PCI bus or the QBus.

PCI configuration cycles may be generated from the QBus by accessing QSpan registers. The cycles proceed as delayed transfers. See "The Register Channel" on page 2-58.

#### 2.1.5 The Interrupt Channel

The QSpan can generate interrupts based on hardware or software events. Two bidirectional interrupt pins are provided: one on the PCI Interface, the other on the QBus Interface. Interrupt registers track the status of errors, and allow users to enable, clear, and map them. Interrupts can also be generated using one of the four available software interrupt sources ("doorbell" interrupts). See "The Interrupt Channel" on page 2-64.

#### 2.1.6 The EEPROM Channel

Certain registers of the QSpan can be programmed by data in an EEPROM at system reset. This allows board designers to set unique identifiers for their cards on the PCI bus at reset, to enable the PCI Bus Expansion ROM Control Register, and set various address and parameters of images. Configuring the QSpan with the EEPROM allows the QSpan to boot-up as a Plug 'n Play compatible device. The QSpan supports reads from and writes to the EEPROM. The EEPROM itself is not included with the QSpan.

### 2.2 The QBus Slave Channel

The QBus is the name given to the bus interfacing with the processor bus. The QBus direct-connects to a QUICC bus, a PowerQUICC bus, or a M68040 bus. The QBus may also be direct-connected to a combination of buses, such as a QUICC bus and a PowerQUICC bus. A QBus master may access a PCI target through the QSpan by using the QBus Slave Channel or the IDMA Channel. This section is concerned with the QBus Slave Channel and is broken down as follows:

- QBus Slave Channel Architecture Overview

- Overview of Channel Description

- Address Phase

- Data Transfer

- Termination Phase

The register section on page 22-62 discusses how to generate PCI configuration cycles from the QBus. The initialization of this channel is discussed in "QBus Slave Channel Initialization" on page D-2.

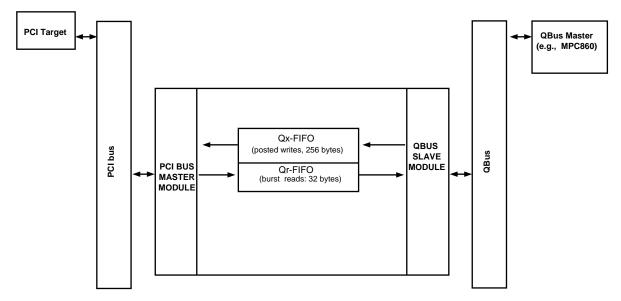

#### 2.2.1 QBus Slave Channel Architecture Overview

In this subsection, the functional architecture of the QBus Slave Channel is briefly presented. The rest of the section deals with the processes involving the channel.

Figure 2.2 QBus Slave Channel in Context

Figure 2.2 depicts the QBus Slave Channel in relation to the QBus and the PCI bus. The QBus is shown as having a PowerQUICC processor and the PCI bus is shown with a single PCI device. The arrows represent data flow. The QBus Slave Channel has the following components:

- The QBus Slave Module

- The Qx-FIFO

- The Qr-FIFO

- The PCI Master Module

The first and last of these components are shared between the QBus Slave Channel and the IDMA channel. These components are discussed in turn.

# 2.2.1.1 QBus Slave Module

The QBus Slave Module is a non-multiplexed 32-bit address, 32-bit data interface. The QBus Slave Module is always capable of accepting QUICC cycles and either PowerQUICC or M68040 cycles. Whether the QBus Slave Module is in PowerQUICC or M68040 mode depends on the value of the SIZ[1] signal at reset. This reset option is presented in Table 2.1. (See also "Reset Options" on page 2-75). The MSTSLV[1:0] field in the MISC\_CTL register indicates the slave (and master) mode of the QBus (page A-46). The connections required for interfacing the QSpan to a QUICC, PowerQUICC, and/or M68040 are given in "Typical Applications" on page C-1.

## Table 2.1 Reset Options for QBus Slave Modes

| Reset sampling of SIZ[1] | Slave Mode              |

|--------------------------|-------------------------|

| 0                        | QUICC and<br>M68040     |

| 1                        | QUICC and<br>PowerQUICC |

# 2.2.1.2 Qx-FIFO and Qr-FIFO

The Qx-FIFO is a 256-byte buffer for posted writes from the QBus to the PCI bus (it can accommodate sixty-four 32-bit entries). The Qx-FIFO can accept data from an external QBus master while sinking data to a PCI target. The Qx-FIFO is described in greater detail in "Writes" on page 2-18.

The Qx-FIFO is on the data path for single delayed writes. A delayed write must be completed before the following write can be posted.

The Qr-FIFO is a 32-byte buffer used to store data read from PCI targets.

# 2.2.1.3 PCI Master Module

The PCI Master Module is a 32 bit/33MHz PCI 2.1 Specification compliant initiator interface. A list of all the PCI signals supported by the QSpan is in "PCI Bus Signals" on page 3-14. Please refer to the PCI 2.1 Specification for more information.

The QSpan requests PCI bus mastership through its PCI Master Module. The PCI Master Module is available to either the QBus Slave Channel (access from a remote QBus master) or the IDMA Channel.

# 2.2.2 Overview of Channel Description

The operation of the QBus Slave Channel is described below by tracing the path of a transaction from the QBus to the PCI bus. This is done by breaking transactions down into three phases:

- Address Phase

- Data Transfer

- Termination Phase

The address phase section describes transaction decoding and how address information from the QBus is passed through to a corresponding address space access on the PCI bus (e.g., how to access memory, I/O or Configuration space on the PCI bus).

The data transfer section describes endian mapping and byte lane translation through the QBus Slave Channel. This section also describes the different ways data is buffered within the QBus Slave Channel depending on the programming of the QBus slave images.

The termination phase section discusses how terminations from the PCI target are communicated back to the master on the QBus. It also describes how the QSpan PCI Master Module handles different terminations (e.g., retries or target-aborts) and the conditions that drive the terminations the QSpan issues as a QBus slave.

# 2.2.3 Address Phase

### 2.2.3.1 Transaction decoding and QBus Slave Images

The QSpan accepts a transaction through its QBus Slave Module when one of its chip selects is asserted along with the Address Strobe ( $\overline{AS}$ ) or Transaction Start signal ( $\overline{TS}$ ). The chip selects, ( $\overline{CSREG}$ ,  $\overline{CSPCI}$ ), need not be detected asserted on the same clock edge as the transaction start signal for QBus Slave Channel accesses. This allows for wait states to be inserted to perform address decoding. However, the IDMA channel requires that  $\overline{CSPCI}$  be detected asserted on the same clock edge as the transaction start signal for dual address IDMA transfers.

Single address IDMA transfers do not require  $\overline{\text{CSPCI}}$  to be asserted.

If  $\overline{\text{CSREG}}$  is asserted, then the transaction is decoded as a QSpan register access (if the address 0x504 is a PCI configuration cycle, see "The Register Channel" on page 2-58). Then the QBus master asserts the PCI chip-select pin ( $\overline{\text{CSPCI}}$ ) and the QBus Slave Module claims the cycle for the QBus Slave Channel, and one of the two QBus slave images is selected. The QBus Slave image is qualified by the IMSEL (Image Select Signal).

The type of PCI cycle that is generated by the QSpan depends both on (a) which QBus slave image is selected, and (b) what type of transaction was initiated by the external QBus master. The level of IMSEL determines which of the two QBus slave images is used. (a) If IMSEL is at a logic 0, QBus Slave Image 0 is selected (see page A-50 and page A-52); if IMSEL is at a logic 1, QBus Slave Image 1 is selected (see page A-53 and page A-55). (b) The levels of BURST and R/W determine whether the QSpan will generate a single PCI cycle or a burst, a PCI read or a write, respectively. (There is some interaction between images and hardware signals, as described on pages A-50 to A-55).

A **slave image** is a set of parameters (encoded in QSpan registers) that control transfers from the QBus to the PCI bus (similar "target" images are provided in the PCI Target Channel). Two QBus slave images of equal capability are provided so that designers can quickly access (on the basis of hardware rather than software) different PCI addresses from the QBus, or access addresses in different ways. The two slave images are completely independent from one another. For example, the designer may set-up QBus Slave Image 0 to access a hard-disk using 128 Mbytes of memory in PCI memory space. The designer could simultaneously have QBus Slave Image 1 available to access a different device, with its own memory size (e.g., 32 Mbytes). For example, the designer would be able to access the first device with posted writes (PWEN = 1), and the other with delayed writes (PWEN = 0). (The PWEN bit has no effect on reads.) For a third type of access, it would be necessary to share one of the slave images.

Table 2.2 and Table 2.3 summarize the QBus slave image control and address fields.

| Field                      | Abbreviation and Register Page | Description                                                       |

|----------------------------|--------------------------------|-------------------------------------------------------------------|

| Block Size                 | BS (page A-52 and page A-55)   | Amount of PCI memory accessed from QBus                           |

| PCI Address Space          | PAS (page A-50 and page A-53)  | Mapping to PCI memory space or I/O space                          |

| Translation Address        | TA (page A-52 and page A-55)   | Address bits that are substituted to generate the PCI bus address |

| Enable Address Translation | EN (page A-52 and page A-55)   | Enables address translation using TA field                        |

Table 2.2

Address Fields for QBus Slave Image

#### Table 2.3 Control Fields for QBus Slave Image

| Field        | Abbreviation and Register Page | Description             |

|--------------|--------------------------------|-------------------------|

| Posted Write | PWEN (page A-50 and page A-53) | Posted write enable bit |

The QBus Slave Channel allows a QBus master to access a range of addresses within PCI Memory or I/O space. The PCI address space bit (PAS) of the selected image determines whether the current transfer is directed towards PCI Memory or I/O space. The range of addresses that can be accessed through a slave image is controlled by the block size field (BS). Up to 2 GBytes of PCI Memory or I/O space can be accessed from the QBus in one slave image if address translation is required. The use of the Block Size, PCI Address Space, Translation Address and Enable Address Translation fields is discussed in "Address Translation" on page 2-12 and "Address Phase on the PCI Bus" on page 2-13.

The QBus Slave Image Control registers allow the user to specify how writes are processed (page A-50 and page A-53). If the PWEN bit is "1", then the QSpan will perform posted writes when that particular QBus slave image is accessed with a single write; otherwise writes are handled as single delayed transactions.

QBus Slave Image 0 can be programmed from an external EEPROM.

The QSpan accepts cycles from QUICC bus masters and either PowerQUICC or M68040 bus masters, as discussed in "QBus Slave Module" on page 2-7. The wait states that the QSpan inserts as a QBus slave are listed in "Wait State Insertion (QBus Slave Module)" on page B-19.

## 2.2.3.1.1 PowerQUICC Cycles

The QSpan behaves as a PowerQUICC slave in response to the assertion of the  $\overline{\text{TS}}$  signal when it is powered-up as a PowerQUICC slave (see "QBus Slave Module" on page 2-7). When the QBus Slave Module receives  $\overline{\text{TS}}$  it always responds with  $\overline{\text{DSACK1/TA}}$ ,  $\overline{\text{TEA}}$ , or  $\overline{\text{HALT/TRETRY}}$ . The QSpan recognizes a transaction as intended for it, and acknowledges it accordingly, only if one of  $\overline{\text{CSREG}}$  or  $\overline{\text{CSPCI}}$  is sampled active in conjunction with  $\overline{\text{TS}}$ . The QSpan samples the address bus and other  $\overline{\text{TS}}$  qualified signals on the same rising edge of QCLK in which it samples  $\overline{\text{TS}}$  asserted.

If  $\overline{\text{BURST/TIP}}$  is asserted at the beginning of the bus cycle (along with the address) the QSpan accepts the incoming cycle as a burst. During bursts, the QSpan monitors  $\overline{\text{BDIP}}$ , which when negated indicates that the current data phase is second last.

When the QSpan is operating as a PowerQUICC slave for non-IDMA transfers, it functions as a 32-bit peripheral and must be addressed as such. External QBus masters must comply with the PowerQUICC timing specification.

# 2.2.3.1.2 QUICC Cycles

The QSpan behaves as a QUICC slave in response to the assertion of the  $\overline{AS}$  signal. When it receives  $\overline{AS}$  it always asserts a subset of  $\overline{DSACK1/TA}$ ,  $\overline{DSACK0}$ ,  $\overline{BERR/TEA}$  and  $\overline{HALT/TRETRY}$ . The QSpan recognizes a transaction as intended for it, and acknowledges it accordingly, only if one of  $\overline{CSREG}$  or  $\overline{CSPCI}$  is sampled active in conjunction with  $\overline{AS}$ . The QSpan does not require that the input signals qualified by  $\overline{AS}$  be valid when  $\overline{AS}$  is asserted—it requires only that they meet the set-up time before the same falling clock edge when  $\overline{AS}$  is first sampled asserted. The QBus Slave Module inserts one wait state during QUICC cycles.

When the QSpan is operating as a QUICC slave, it functions as a 32-bit peripheral in synchronous mode. As a master, the QSpan also operates synchronously and therefore the BSTM bit in the QUICC should be set to a "1". External QBus masters must comply with the QUICC timing specification.

## 2.2.3.1.3 M68040 Cycles

The QSpan behaves as a M68040 slave in response to the assertion of the  $\overline{\text{TS}}$  signal when it is powered-up as a M68040 slave (see "QBus Master and Slave Modes" on page 2-77). When the QBus Slave Module receives  $\overline{\text{TS}}$  it always responds with  $\overline{\text{DSACK1/TA}}$  or  $\overline{\text{BERR/TEA}}$ . The QSpan recognizes a transaction as intended for it, and acknowledges it accordingly, only if one of  $\overline{\text{CSREG}}$  or  $\overline{\text{CSPCI}}$  is sampled active in conjunction with  $\overline{\text{TS}}$ . The QSpan samples the address bus and other  $\overline{\text{TS}}$  qualified signals on the same rising edge of QCLK in which it samples  $\overline{\text{TS}}$  asserted. The QBus Slave Module accepts bursting of incoming data.

When the QSpan is operating as a M68040 slave, it functions as a 32-bit peripheral in synchronous mode and must be addressed as such. External QBus masters must comply with the M68040 timing specification.

### 2.2.3.2 PCI Bus Request

The PCI Master Module requests the PCI bus when write data is received in the Qx-FIFO, the last data phase of a burst write has been received in the Qx-FIFO, or if there is a read request. When the QSpan requires control of the PCI bus it asserts REQ# and gains bus mastership when the PCI arbiter asserts GNT#. If the arbiter removes GNT# after the QSpan has begun its PCI transaction, the QSpan completes the current cycle and releases the PCI bus. This means that the QSpan PCI Master Module will have to re-arbitrate for the PCI bus after every cycle if its GNT# is removed. The QSpan performance as PCI master can be enhanced through bus parking, as defined in the PCI 2.1 Specification (GNT# asserted to the QSpan by the PCI bus arbiter).

The QSpan cannot be both Master and target on the PCI bus at the same time.

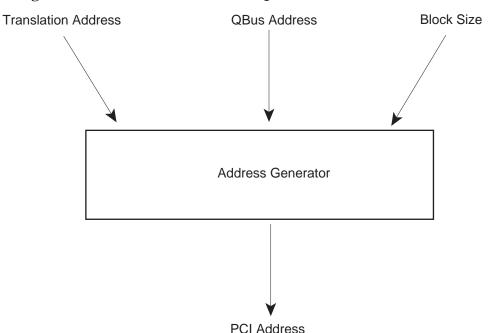

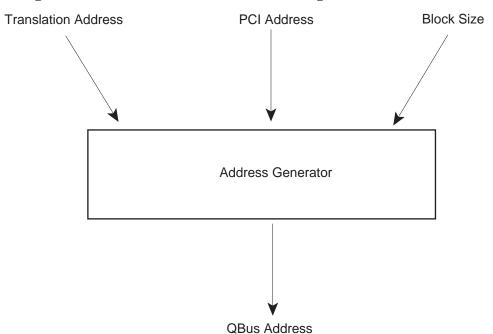

### 2.2.3.3 Address Translation

The QBus Slave Channel contains an Address Generator (see Figure 2.3 below) which is used if address translation is enabled (EN bit in Table A.42 or Table A.47). The Address Generator produces the PCI address using three inputs: the address of the QBus signal (A[31:0]), the block size of the QBus slave image (BS field of the QBSIx\_AT register), and the translation address of the QBus slave image (TA field of the QBSIx\_AT register). The translation address is a 16-bit number whose upper bits specify the location of the slave image on the PCI bus. The correlation between BS and the number of TA bits to use in generating the PCI address is shown in Table 2.4 on page 22-13. For example, with a 64 KByte block size, the Address Generator copies the entire translation address into the PCI address and only copies the lower 16 bits from the QBus address signals—i.e., the Address Generator translates A[31:16] and copies A[15:0] from the QBus. With a 2 GByte block size, the Address Generator copies all but bit 31 from the QBus address signal (i.e., the Address Generator translates A[31] only while copying A[30:0]), and uses the top translation address bit as bit 31 of the PCI address.

Figure 2.3 Address Generator for QBus Slave Channel Transfers

| BS in QBSI0_CTL or<br>QBSI1_CTL | Block Size | Address Lines<br>Translated | Translation Address Bits<br>Copied |

|---------------------------------|------------|-----------------------------|------------------------------------|

| 0000                            | 64K        | A31-A16                     | TA31-TA16                          |

| 0001                            | 128K       | A31-A17                     | TA31-TA17                          |

| 0010                            | 256K       | A31-A18                     | TA31-TA18                          |

| 0011                            | 512K       | A31-A19                     | TA31-TA19                          |

| 0100                            | 1 <b>M</b> | A31-A20                     | TA31-TA20                          |

| 0101                            | 2M         | A31-A21                     | TA31-TA21                          |

| 0110                            | 4M         | A31-A22                     | TA31-TA22                          |

| 0111                            | 8M         | A31-A23                     | TA31-TA23                          |

| 1000                            | 16M        | A31-A24                     | TA31-TA24                          |

| 1001                            | 32M        | A31-A25                     | TA31-TA25                          |

| 1010                            | 64M        | A31-A26                     | TA31-TA26                          |

| 1011                            | 128M       | A31-A27                     | TA31-TA27                          |

| 1100                            | 256M       | A31-A28                     | TA31-TA28                          |

| 1101                            | 512M       | A31-A29                     | TA31-TA29                          |

| 1110                            | 1 <b>G</b> | A31-A30                     | TA31-TA30                          |

| 1111                            | 2G         | A31                         | TA31                               |

Table 2.4

Translation of QBus Address to PCI Address

This manual adopts the convention that the most significant bit (address or data) is always the largest number. PowerQUICC designers must ensure that they connect their pins accordingly: e.g., pin A[31] on the QSpan connects to pin A[31] on the QUICC bus, but connects to pin A[0] on the PowerQUICC bus. This applies to all PowerQUICC buses (D[31:0], AT[3:0], TSIZ[1:0]) not only the address bus.

### 2.2.3.4 Address Phase on the PCI Bus

The address supplied on the AD[31:0] lines on the PCI bus is the result of the address translation described above. The PCI command encoding on the C/BE#[3:0] lines is determined by the type of transaction on the QBus and the programming of the PAS bit in the QBus Slave Image Control Register (page A-50 or page A-53).

Table 2.5 lists the C/BE encoding supported by the QSpan.

Table 2.6 below shows the mapping from QBus transaction type to PCI transaction type as a function of PAS programming.

| C/BE# [3:0] | Command Type                | QSpan Capability                               |

|-------------|-----------------------------|------------------------------------------------|

| 0000        | Interrupt Acknowledge       | See "Interrupt Acknowledge Cycle" on page 2-68 |

| 0001        | Special Cycle               | N/A                                            |

| 0010        | I/O Read                    | Target/Master                                  |

| 0011        | I/O Write                   | Target/Master                                  |

| 0100        | Reserved                    | N/A                                            |

| 0101        | Reserved                    | N/A                                            |

| 0110        | Memory Read                 | Target/Master                                  |

| 0111        | Memory Write                | Target/Master                                  |

| 1000        | Reserved                    | N/A                                            |

| 1001        | Reserved                    | N/A                                            |

| 1010        | Configuration Read          | Target/Master                                  |

| 1011        | Configuration Write         | Target/Master                                  |

| 1100        | Memory Read Multiple        | Master                                         |

| 1101        | Dual Address Cycle          | N/A                                            |

| 1110        | Memory Read Line            | Master for IDMA transfer                       |

| 1111        | Memory Write and Invalidate | Master for IDMA transfer                       |

Table 2.5

Command Type Encoding for Transfer Type

PCI targets are expected to assert DEVSEL# if they have decoded the access. If a target does not respond with DEVSEL# within 6 clocks, a Master-Abort is generated by the QSpan.

Table 2.6

Translation from QBus Transaction to PCI Transaction Type

| QBus transaction received | PAS bit programming | PCI transaction type |

|---------------------------|---------------------|----------------------|

| Single or Burst Read      | Memory              | Memory Read          |

| Single Read               | I/O                 | I/O Read             |

| Burst Read                | I/O                 | None <sup>a</sup>    |

| Single or Burst Write     | Memory              | Memory Write         |

| Single Write              | I/O                 | I/O Write            |

| Burst Write               | I/O                 | None <sup>a</sup>    |

a. In this case an error is signalled on the QBus.

# 2.2.4 Data Transfer

This section describes how endian mapping is executed in the QBus Slave Channel; it also discusses the data path for different transaction types.

## 2.2.4.1 Endian Mapping

The PCI bus and the Motorola processors have some differences in the way they order and address bytes. These differences are explained in Appendix E. The present section describes how the QSpan translates cycles from the QBus to the PCI bus.

The PCI bus is always a Little-Endian environment. The QBus may be configured as Little-Endian or Big-Endian, depending on the value of the QBus Byte Ordering Control bit (QB\_BOC) in the MISC\_CTL register (page A-46). The default mode for the QBus is Big-Endian. The QSpan translates byte lane ordering when the QBus is Big-Endian, while preserving the addressing of bytes. When the QBus is Little-Endian (according to QB\_BOC), the QSpan preserves byte lane ordering, while translating the addressing of bytes. Note that the QB\_BOC bit affects transactions in all channels.